# UM2010 用户手册

版本: V1.4

UNICMICRO

广芯微电子

广芯微电子（广州）股份有限公司

<http://www.unicmicro.com/>

## 条款协议

本文档的所有部分，其著作产权归广芯微电子（广州）股份有限公司（以下简称广芯微电子）所有，未经广芯微电子授权许可，任何个人及组织不得复制、转载、仿制本文档的全部或部分组件。本文档没有任何形式的担保、立场表达或其他暗示，若有任何因本文档或其中提及的产品所有资讯所引起的直接或间接损失，广芯微电子及所属员工恕不为其担保任何责任。除此以外，本文档所提到的产品规格及资讯仅供参考，内容亦会随时更新，恕不另行通知。

1. 本文档中所记载的关于电路、软件和其他相关信息仅用于说明半导体产品的操作和应用实例。用户如在设备设计中应用本文档中的电路、软件和相关信息，请自行负责。对于用户或第三方因使用上述电路、软件或信息而遭受的任何损失，广芯微电子不承担任何责任。

2. 在准备本文档所记载的信息的过程中，广芯微电子已尽量做到合理注意，但是，广芯微电子并不保证这些信息都是准确无误的。用户因本文档中所记载的信息的错误或遗漏而遭受的任何损失，广芯微电子不承担任何责任。

3. 对于因使用本文档中的广芯微电子产品或技术信息而造成的侵权行为或因此而侵犯第三方的专利、版权或其他知识产权的行为，广芯微电子不承担任何责任。本文档所记载的内容不应视为对广芯微电子或其他人所有的专利、版权或其他知识产权作出任何明示、默示或其它方式的许可及授权。

4. 使用本文档中记载的广芯微电子产品时，应在广芯微电子指定的范围内，特别是在最大额定值、电源工作电压范围、热辐射特性、安装条件以及其他产品特性的范围内使用。对于在上述指定范围之外使用广芯微电子产品而产生的故障或损失，广芯微电子不承担任何责任。

5. 虽然广芯微电子一直致力于提高广芯微电子产品的质量和可靠性，但是，半导体产品有其自身的特点，如一定的故障发生率以及在某些使用条件下会发生故障等。此外，广芯微电子产品均未进行防辐射设计。所以请采取安全保护措施，以避免当广芯微电子产品在发生故障而造成火灾时导致人身事故、伤害或损害的事故。例如进行软硬件安全设计（包括但不限于冗余设计、防火控制以及故障预防等）、适当的老化处理或其他适当的措施等。

## 目录

|      |                                   |    |

|------|-----------------------------------|----|

| 1    | 系统概述                              | 1  |

| 2    | 功能框图                              | 2  |

| 3    | 封装及管脚描述                           | 3  |

| 3.1  | 封装管脚分布                            | 3  |

| 3.2  | 引脚功能描述                            | 3  |

| 4    | 寄存器定义                             | 5  |

| 4.1  | Reg00 Address: 0x00 Default: 0x1D | 5  |

| 4.2  | Reg01 Address: 0x01 Default: 0x78 | 5  |

| 4.3  | Reg02 Address: 0x02 Default: 0x00 | 5  |

| 4.4  | Reg03 Address: 0x03 Default: 0x00 | 6  |

| 4.5  | Reg04 Address: 0x04 Default: 0x00 | 6  |

| 4.6  | Reg05 Address: 0x05 Default: 0x03 | 6  |

| 4.7  | Reg06 Address: 0x06 Default: 0x33 | 6  |

| 4.8  | Reg07 Address: 0x07 Default: 0x33 | 6  |

| 4.9  | Reg08 Address: 0x08 Default: 0x10 | 7  |

| 4.10 | Reg09 Address: 0x09 Default: 0x00 | 7  |

| 4.11 | Reg0A Address: 0x0A Default: 0x00 | 7  |

| 4.12 | Reg0B Address: 0x0B Default: 0x00 | 7  |

| 4.13 | Reg0C Address: 0x0C Default: 0x50 | 7  |

| 4.14 | Reg0D Address: 0x0D Default: 0x30 | 8  |

| 4.15 | Reg0E Address: 0x0E Default: 0x32 | 8  |

| 4.16 | Reg10 Address: 0x10 Default: 0x40 | 9  |

| 4.17 | Reg11 Address: 0x11 Default: 0x00 | 10 |

| 4.18 | Reg1D Address: 0x1D Default: 0x80 | 10 |

| 4.19 | Reg20 Address: 0x20 Default: 0x50 | 11 |

| 4.20 | Reg21 Address: 0x21 Default: 0x60 | 11 |

| 4.21 | Reg27 Address: 0x27 Default: 0x60 | 11 |

| 4.22 | Reg28 Address: 0x28 Default: 0x19 | 12 |

| 4.23 | Reg2B Address: 0x2B Default: 0xFF | 12 |

| 4.24 | Reg2C Address: 0x2C Default: 0xFF | 12 |

| 4.25 | Reg2D Address: 0x2D Default: 0x10 | 13 |

| 4.26 | Reg30 Address: 0x30 Default: 0x80 | 13 |

| 4.27 | Reg31 Address: 0x31 Default: 0x66 | 13 |

| 4.28 | Reg37 Address: 0x37 Default: 0x06 | 14 |

| 4.29 | Reg38 Address: 0x38 Default: 0x91 | 14 |

|      |                                   |    |

|------|-----------------------------------|----|

| 4.30 | Reg4D Address: 0x4D Default: 0x10 | 14 |

| 4.31 | Reg4E Address: 0x4E Default: 0x45 | 15 |

| 4.32 | Reg4F Address: 0x4F Default: 0x67 | 15 |

| 4.33 | Reg50 Address: 0x50 Default: 0x00 | 16 |

| 4.34 | Reg51 Address: 0x51 Default: 0x00 | 16 |

| 4.35 | Reg52 Address: 0x52 Default: 0x00 | 16 |

| 4.36 | Reg53 Address: 0x53 Default: 0x00 | 16 |

| 4.37 | Reg54 Address: 0x54 Default: 0x00 | 16 |

| 4.38 | Reg55 Address: 0x55 Default: 0x00 | 17 |

| 4.39 | Reg56 Address: 0x56 Default: 0xB7 | 17 |

| 4.40 | Reg57 Address: 0x57 Default: 0x00 | 17 |

| 4.41 | Reg58 Address: 0x58 Default: 0x00 | 17 |

| 4.42 | Reg5D Address: 0x5D Default: 0x00 | 18 |

| 4.43 | Reg60 Address: 0x60 Default: 0x80 | 18 |

| 4.44 | Reg61 Address: 0x61 Default: 0x00 | 18 |

| 4.45 | Reg64 Address: 0x64 Default: 0x00 | 19 |

| 4.46 | Reg67 Address: 0x67 Default: 0x80 | 19 |

| 4.47 | Reg68 Address: 0x68 Default: 0x00 | 19 |

| 4.48 | Reg69 Address: 0x69 Default: 0x00 | 19 |

| 4.49 | Reg6A Address: 0x6A Default: 0x00 | 20 |

| 4.50 | Reg6B Address: 0x6B Default: 0x00 | 20 |

| 4.51 | Reg6C Address: 0x6C Default: 0x00 | 20 |

| 4.52 | Reg6D Address: 0x6D Default: 0x00 | 20 |

| 4.53 | Reg6E Address: 0x6E Default: 0x00 | 20 |

| 4.54 | Reg6F Address: 0x6F Default: 0x00 | 21 |

| 4.55 | Reg70 Address: 0x70 Default: 0xFF | 21 |

| 4.56 | Reg71 Address: 0x71 Default: 0x09 | 21 |

| 4.57 | Reg72 Address: 0x72 Default: 0x01 | 21 |

| 4.58 | Reg73 Address: 0x73 Default: 0x55 | 22 |

| 4.59 | Reg74 Address: 0x74 Default: 0x03 | 22 |

| 4.60 | Reg75 Address: 0x75 Default: 0xA7 | 23 |

| 4.61 | Reg76 Address: 0x76 Default: 0xA7 | 23 |

| 4.62 | Reg77 Address: 0x77 Default: 0x98 | 23 |

| 4.63 | Reg78 Address: 0x78 Default: 0xF3 | 23 |

| 4.64 | Reg79 Address: 0x79 Default: 0x98 | 23 |

| 4.65 | Reg7A Address: 0x7A Default: 0xF3 | 23 |

| 4.66 | Reg7B Address: 0x7B Default: 0x98 | 24 |

| 4.67 | Reg7C Address: 0x7C Default: 0xF3 | 24 |

|       |                                   |    |

|-------|-----------------------------------|----|

| 4.68  | Reg7D Address: 0x7D Default: 0x0E | 24 |

| 4.69  | Reg7E Address: 0x7E Default: 0x00 | 24 |

| 4.70  | Reg7F Address: 0x7F Default: 0x00 | 24 |

| 4.71  | Reg80 Address: 0x80 Default: 0x1D | 25 |

| 4.72  | Reg81 Address: 0x81 Default: 0x78 | 25 |

| 4.73  | Reg82 Address: 0x82 Default: 0x00 | 26 |

| 4.74  | Reg83 Address: 0x83 Default: 0x00 | 26 |

| 4.75  | Reg84 Address: 0x84 Default: 0x00 | 26 |

| 4.76  | Reg85 Address: 0x85 Default: 0x03 | 26 |

| 4.77  | Reg86 Address: 0x86 Default: 0x33 | 26 |

| 4.78  | Reg87 Address: 0x87 Default: 0x33 | 27 |

| 4.79  | Reg88 Address: 0x88 Default: 0x10 | 27 |

| 4.80  | Reg89 Address: 0x89 Default: 0x00 | 27 |

| 4.81  | Reg8A Address: 0x8A Default: 0x00 | 27 |

| 4.82  | Reg8B Address: 0x8B Default: 0x00 | 28 |

| 4.83  | Reg8C Address: 0x8C Default: 0x50 | 28 |

| 4.84  | Reg8D Address: 0x8D Default: 0x30 | 28 |

| 4.85  | Reg8E Address: 0x8E Default: 0x32 | 28 |

| 4.86  | Reg94 Address: 0x94 Default: 0x08 | 28 |

| 4.87  | Reg95 Address: 0x95 Default: 0x20 | 29 |

| 4.88  | Reg96 Address: 0x96 Default: 0x26 | 29 |

| 4.89  | Reg97 Address: 0x97 Default: 0x1F | 29 |

| 4.90  | Reg98 Address: 0x98 Default: 0x68 | 29 |

| 4.91  | Reg99 Address: 0x99 Default: 0x04 | 30 |

| 4.92  | Reg9A Address: 0x9A Default: 0xAE | 30 |

| 4.93  | Reg9B Address: 0x9B Default: 0x89 | 30 |

| 4.94  | Reg9C Address: 0x9C Default: 0x84 | 30 |

| 4.95  | Reg9D Address: 0x9D Default: 0x03 | 30 |

| 4.96  | Reg9E Address: 0x9E Default: 0x80 | 31 |

| 4.97  | Reg9F Address: 0x9F Default: 0x26 | 31 |

| 4.98  | RegA0 Address: 0xA0 Default: 0x50 | 31 |

| 4.99  | RegA3 Address: 0xA3 Default: 0x42 | 31 |

| 4.100 | RegE0 Address: 0xE0 Default: 0x80 | 32 |

| 4.101 | RegE1 Address: 0xE1 Default: 0x00 | 32 |

| 4.102 | RegE2 Address: 0xE2 Default: 0x01 | 32 |

| 4.103 | RegE3 Address: 0xE3 Default: 0x40 | 32 |

| 5     | 功能描述                              | 33 |

| 5.1   | 接收机                               | 33 |

|       |               |    |

|-------|---------------|----|

| 5.2   | 发射机           | 33 |

| 5.3   | 系统复位          | 34 |

| 5.3.1 | POR复位         | 34 |

| 5.3.2 | 外部复位          | 34 |

| 5.3.3 | 软件复位          | 35 |

| 5.4   | 频率综合器         | 35 |

| 5.5   | 晶体振荡器         | 37 |

| 5.6   | AGC           | 38 |

| 5.7   | RSSI          | 38 |

| 5.7.1 | 自动计算RSSI      | 39 |

| 5.7.2 | 手动调节增益        | 40 |

| 5.7.3 | RSSI自动过滤功能    | 41 |

| 5.8   | AFC           | 41 |

| 6     | 芯片运行          | 42 |

| 6.1   | SPI接口         | 42 |

| 6.2   | FIFO          | 43 |

| 6.2.1 | FIFO的工作模式     | 44 |

| 6.2.2 | FIFO的中断时序     | 44 |

| 6.2.3 | FIFO的应用场景     | 44 |

| 6.3   | GPIO和中断       | 46 |

| 6.4   | 启动时序和状态机      | 49 |

| 6.4.1 | 状态机控制图        | 49 |

| 6.4.2 | 工作模式          | 50 |

| 6.4.3 | 状态机说明         | 50 |

| 7     | 数据包及包处理机制     | 52 |

| 7.1   | 直通模式 (Direct) | 52 |

| 7.1.1 | 直通模式操作流程      | 53 |

| 7.2   | 数据包 (Packet)  | 53 |

| 7.2.1 | 数据包模式         | 54 |

| 7.2.2 | 数据包操作流程       | 56 |

| 7.2.3 | 数据包字段         | 57 |

| 8     | 典型应用          | 75 |

| 8.1   | 参考原理图         | 75 |

| 8.2   | +13dBm匹配参数    | 76 |

| 8.3   | +18dBm匹配参数    | 77 |

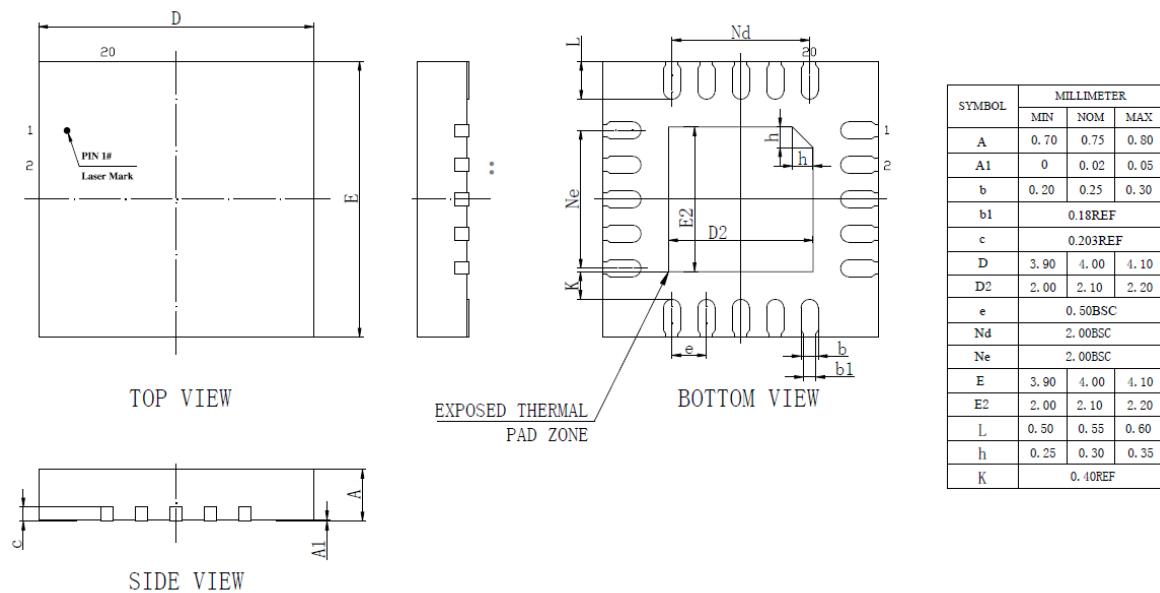

| 9     | 封装尺寸          | 78 |

| 9.1   | QFN20 (4*4mm) | 78 |

|               |    |

|---------------|----|

| 10 版本维护 ..... | 79 |

|---------------|----|

unicmicro

## 表目录

|                               |    |

|-------------------------------|----|

| 表 5-1: 外部复位相关寄存器.....         | 35 |

| 表 5-2: 软复位相关寄存器.....          | 35 |

| 表 5-3: 频率综合器相关寄存器.....        | 36 |

| 表 5-4: 晶振相关寄存器 .....          | 37 |

| 表 5-5: AGC相关寄存器 .....         | 38 |

| 表 5-6: RSSI相关寄存器列表.....       | 38 |

| 表 5-7: Reg2B增益控制表.....        | 40 |

| 表 5-8: AFC相关寄存器.....          | 41 |

| 表 6-1: SPI时序参数 .....          | 43 |

| 表 6-2: SPI相关寄存器.....          | 43 |

| 表 6-3: FIFO相关寄存器列表.....       | 44 |

| 表 6-4: GPIO配置相关寄存器列表 .....    | 47 |

| 表 6-5: GPIO输出功能描述 .....       | 48 |

| 表 6-6: 工作模式表 .....            | 50 |

| 表 7-1: Direct相关寄存器列表.....     | 52 |

| 表 7-2: Mode相关寄存器列表.....       | 54 |

| 表 7-3: Preamble配置相关寄存器列表..... | 57 |

| 表 7-4: Sync配置相关寄存器列表 .....    | 58 |

| 表 7-5: Payload相关寄存器 .....     | 60 |

| 表 7-6: Length相关的寄存器列表.....    | 63 |

| 表 7-7: Address配置相关寄存器列表 ..... | 68 |

| 表 7-8: seqnum相关的寄存器列表 .....   | 69 |

| 表 7-9: FCS2相关的寄存器列表.....      | 70 |

| 表 7-10: CRC相关的寄存器列表.....      | 71 |

| 表 7-11: 常用CRC标准和多项式列表 .....   | 73 |

| 表 8-1: +13dBm匹配参考参数表.....     | 76 |

| 表 8-2: 天线匹配参考参数表.....         | 77 |

## 图目录

|                                                |    |

|------------------------------------------------|----|

| 图 2-1: 功能框图 .....                              | 2  |

| 图 5-1: POR复位时序图 .....                          | 34 |

| 图 5-2: RSSI线性图 .....                           | 40 |

| 图 6-1: SPI读写寄存器时序图 .....                       | 42 |

| 图 6-2: SPI读写FIFO时序图 .....                      | 43 |

| 图 6-3: 状态机控制图 .....                            | 49 |

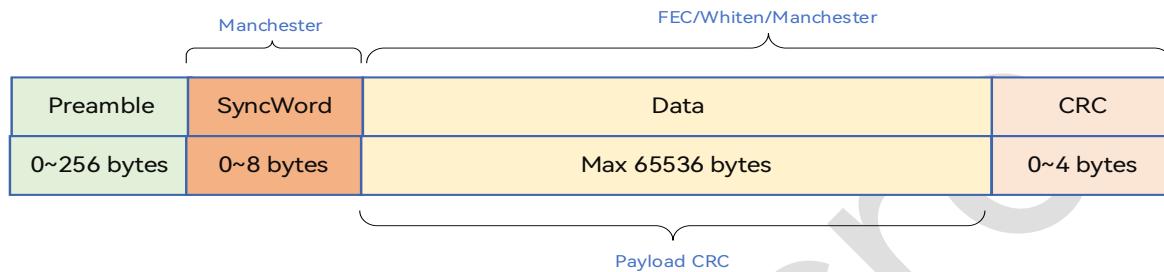

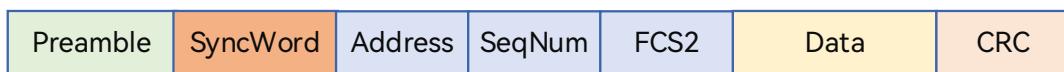

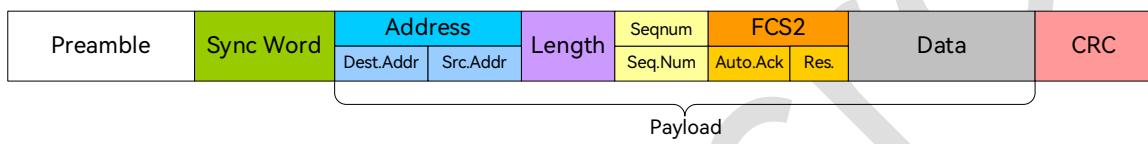

| 图 7-1: Mode 0帧格式 .....                         | 54 |

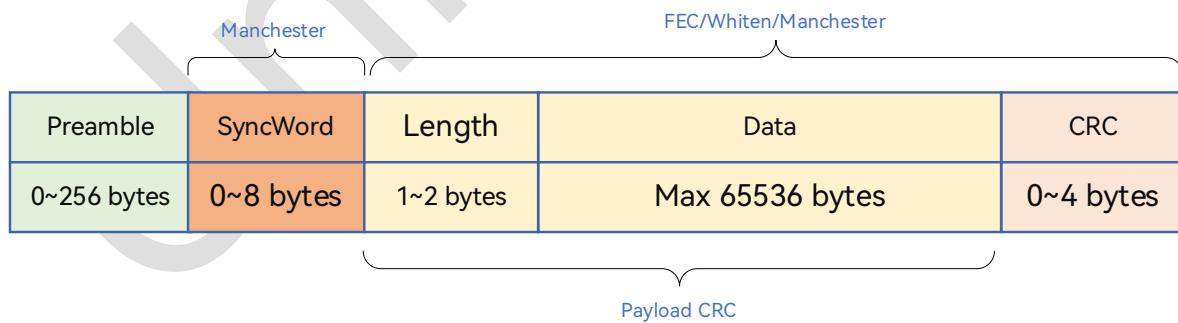

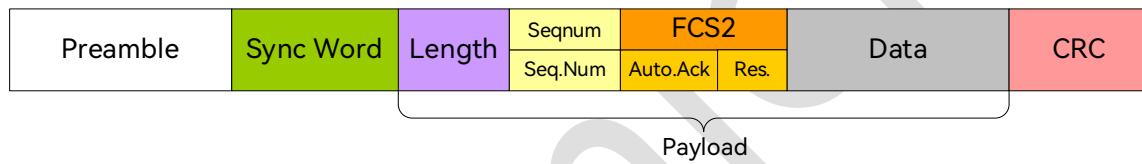

| 图 7-2: Mode 1帧格式 .....                         | 55 |

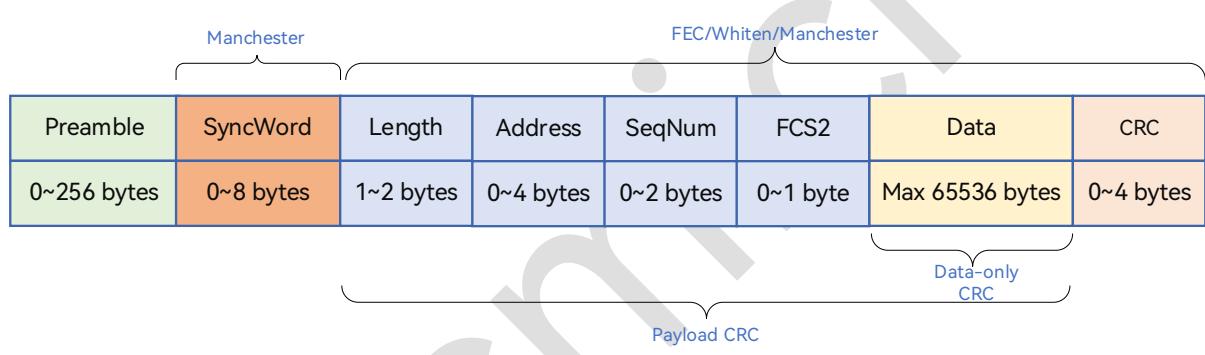

| 图 7-3: Mode 2帧格式 .....                         | 55 |

| 图 7-4: Mode 3帧格式 .....                         | 56 |

| 图 7-5: PAYLOAD_BIT_ORDER操作 .....               | 61 |

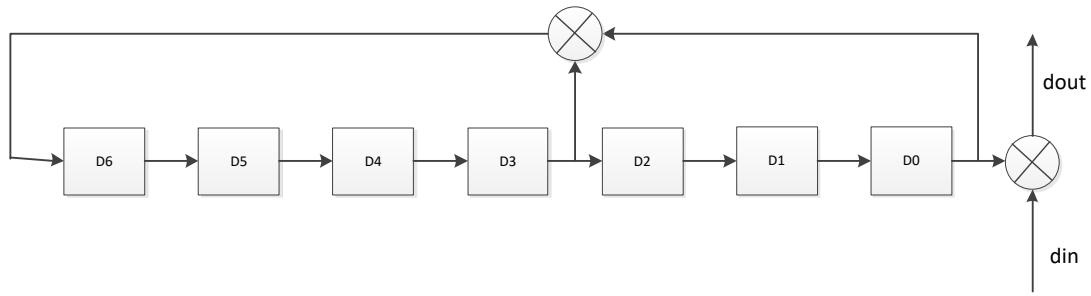

| 图 7-6: PN7抽出模式移位顺序 .....                       | 62 |

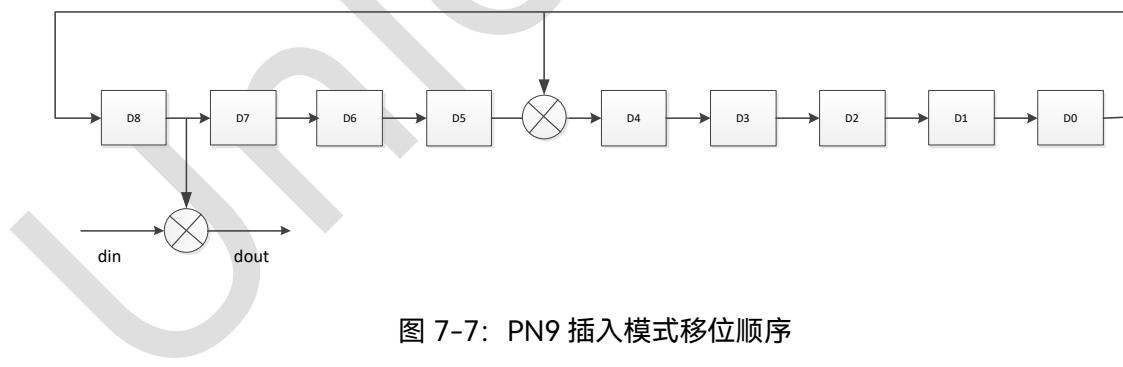

| 图 7-7: PN9插入模式移位顺序 .....                       | 62 |

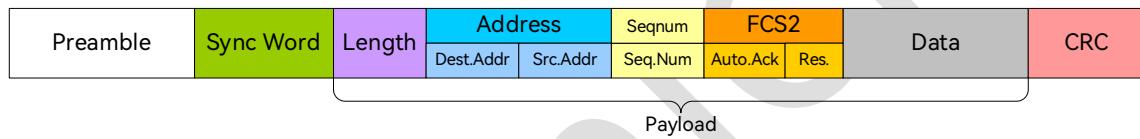

| 图 7-8: m3_length_en=0时MODE 3帧格式 .....          | 64 |

| 图 7-9: 可变长度包格式, Address不存在 .....               | 65 |

| 图 7-10: Address存在, Address在Length Byte之前 ..... | 66 |

| 图 7-11: Address存在, Address在Length Byte之后 ..... | 67 |

| 图 7-12: ACK的包格式 .....                          | 71 |

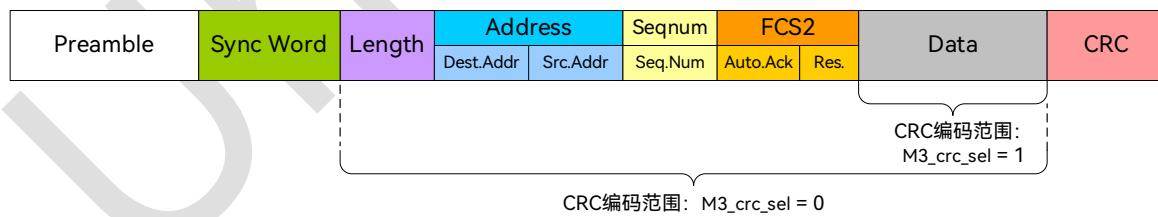

| 图 7-13: CRC编码范围 .....                          | 72 |

| 图 7-14: CRC_INV .....                          | 73 |

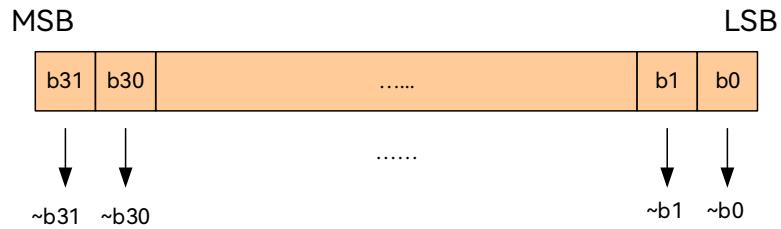

| 图 7-15: CRC_BIT_ORDER .....                    | 73 |

| 图 7-16: CRC8的配置示例 .....                        | 74 |

| 图 7-17: CRC16的配置示例 .....                       | 74 |

| 图 8-1: 应用参考原理图 .....                           | 75 |

| 图 9-1: QFN20封装图 .....                          | 78 |

# 1 系统概述

UM2010 是一款工作于 200MHz~960MHz 范围内的低功耗、高性能、单片集成的(G)FSK/OOK 无线收发机芯片。内部集成完整的射频接收机、射频发射机、频率综合器、调制解调器，只需配备简单、低成本的外围器件就可以获得良好的收发性能。

芯片支持灵活可设的数据包格式，支持自动应答和自动重发功能，支持跳频操作，同时集成了 FEC 功能。外部 MCU 可通过 SPI 对芯片进行控制，并访问内部收发各 128 bytes 的 TX/RX FIFO。

## 典型应用：

- 工业传感及工业控制

- 安防系统

- 自动抄表

- 无线标签，无线门禁

- 遥控装置，无线玩具

- 智能交通，智慧城市，智能家居

- 智能门锁，资产追踪、无线监控等智能传感器终端应用

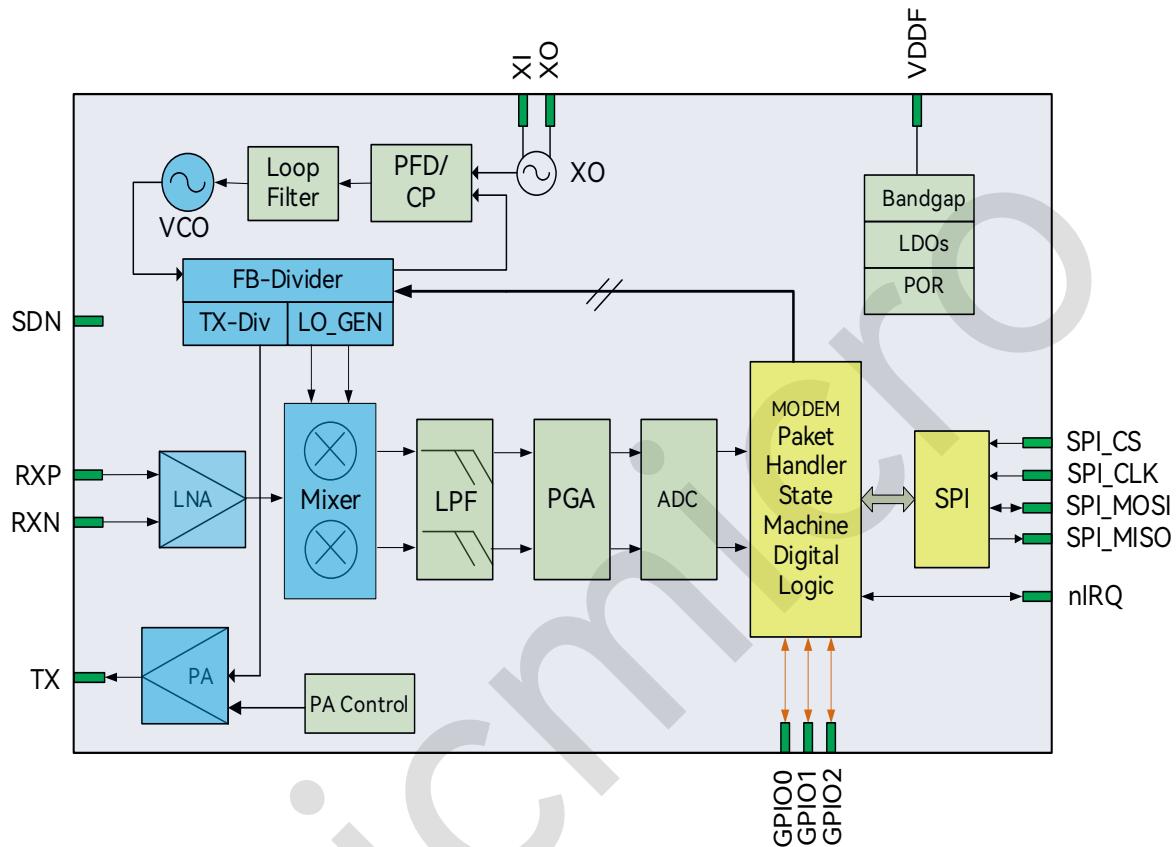

## 2 功能框图

图 2-1: 功能框图

# 3 封装及管脚描述

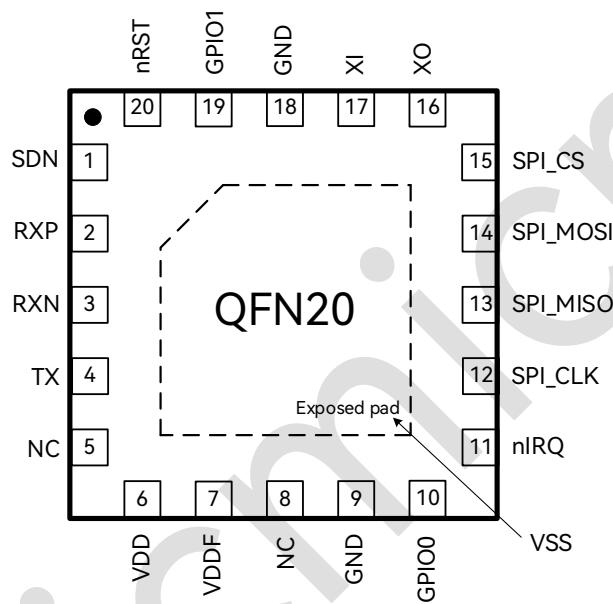

## 3.1 封装管脚分布

图 3-1: QFN20 封装管脚分布图

## 3.2 引脚功能描述

表 3-1: 引脚功能说明

| 引脚编号 | 管脚名称 | IO 类型 | 关断状态 | 功能描述                     |

|------|------|-------|------|--------------------------|

| 0    | VSS  | G     | -    | 芯片地(LF PAD)公共地           |

| 1    | SDN  | DI    | HZ   | 芯片关断使能, SDN 高电平时芯片处于关断模式 |

| 2    | RXP  | RFI   | -    | 射频正端输入                   |

| 3    | RXN  | RFI   | -    | 射频负端输入                   |

| 4    | TX   | RFO   | -    | 射频 PA 输出                 |

| 5    | NC   | NC    | -    | 空脚, 未连接任何内部电路            |

| 6    | VDD  | P     | -    | 1.8V~3.6V 电源输入           |

| 7    | VDDF | P     | -    | RF LDO 供电电源              |

| 引脚编号 | 管脚名称     | IO 类型 | 关断状态 | 功能描述                 |

|------|----------|-------|------|----------------------|

| 8    | NC       | NC    | -    | 空脚, 未连接任何内部电路        |

| 9    | GND      | G     | -    | 芯片地                  |

| 10   | GPIO0    | DIO   | HZ   | 可配置 GPIO0            |

| 11   | nIRQ     | DIO   | HZ   | 可配置 GPIO, 默认为中断输出    |

| 12   | SPI_CLK  | DI    | HZ   | SPI 时钟               |

| 13   | SPI_MISO | DO    | HZ   | SPI 数据输出             |

| 14   | SPI_MOSI | DIO   | HZ   | SPI 数据输入 (或三线制输入输出)  |

| 15   | SPI_CS   | DI    | HZ   | 片选信号                 |

| 16   | XO       | AO    | -    | 晶振输出                 |

| 17   | XI       | AI    | -    | 晶振输入                 |

| 18   | GND      | G     | -    | 芯片地                  |

| 19   | GPIO1    | DIO   | HZ   | 可配置 GPIO1            |

| 20   | nRST     | DIO   | HZ   | 可配置 GPIO2, 默认为外部复位引脚 |

说明: RF——射频信号; A——模拟信号; D——数字信号; I——Input; O——Output; G——Ground;

P——Power; PU——pull up 上拉; PD——pull down 下拉; HZ——高阻状态。

## 4 寄存器定义

### 4.1 Reg00 Address: 0x00 Default: 0x1D

| Bit | Name         | Type | Description                                                                                                                                                                                                            | Default |

|-----|--------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 7   | reserved     | R/W  | -                                                                                                                                                                                                                      | 1'b0    |

| 6:0 | rf_f0[30:24] | R/W  | 信道频率 f0[30:24]。<br>信道频率 rf_freq 设置公式：<br>$rf\_freq=rf\_f0+ch\_num*f\_step$<br>rf_f0 由{Reg00,Reg01,Reg02,Reg03}配置, 单位为 MHz, 低 20 位为小数;<br>ch_num 由 Reg04 配置;<br>步进频率 f_step 由{Reg05,Reg06,Reg07}配置, 单位为 MHz, 低 20 位为小数。 | 7'h1D   |

### 4.2 Reg01 Address: 0x01 Default: 0x78

| Bit | Name         | Type | Description    | Default |

|-----|--------------|------|----------------|---------|

| 7:0 | rf_f0[23:16] | R/W  | 信道频率 f0[23:16] | 8'h78   |

### 4.3 Reg02 Address: 0x02 Default: 0x00

| Bit | Name        | Type | Description   | Default |

|-----|-------------|------|---------------|---------|

| 7:0 | rf_f0[15:8] | R/W  | 信道频率 f0[15:8] | 8'h00   |

## 4.4 Reg03 Address: 0x03 Default: 0x00

| Bit | Name       | Type | Description  | Default |

|-----|------------|------|--------------|---------|

| 7:0 | rf_f0[7:0] | R/W  | 信道频率 f0[7:0] | 8'h00   |

## 4.5 Reg04 Address: 0x04 Default: 0x00

| Bit | Name   | Type | Description             | Default |

|-----|--------|------|-------------------------|---------|

| 7:0 | ch_num | R/W  | 信道号 ch_num, 参考 Reg00 描述 | 8'h00   |

## 4.6 Reg05 Address: 0x05 Default: 0x03

| Bit | Name          | Type | Description                                              | Default |

|-----|---------------|------|----------------------------------------------------------|---------|

| 7:0 | f_step[23:16] | R/W  | 信道步进频率 f_step[23:16], 单位为 MHz,<br>低 20 位为小数, 参考 Reg00 描述 | 8'h03   |

## 4.7 Reg06 Address: 0x06 Default: 0x33

| Bit | Name         | Type | Description                      | Default |

|-----|--------------|------|----------------------------------|---------|

| 7:0 | f_step[15:8] | R/W  | 信道步进频率 f_step[15:8], 参考 Reg00 描述 | 8'h33   |

## 4.8 Reg07 Address: 0x07 Default: 0x33

| Bit | Name        | Type | Description                     | Default |

|-----|-------------|------|---------------------------------|---------|

| 7:0 | f_step[7:0] | R/W  | 信道步进频率 f_step[7:0], 参考 Reg00 描述 | 8'h33   |

## 4.9 Reg08 Address: 0x08 Default: 0x10

| Bit | Name            | Type | Description                                                                          | Default |

|-----|-----------------|------|--------------------------------------------------------------------------------------|---------|

| 7   | Reserved        | R/W  | -                                                                                    | 1'b0    |

| 6:0 | ref_freq[30:24] | R/W  | 参考频率（晶振频率）设置, ref_freq 由 {Reg08[6:0],Reg09,Reg0A,Reg0B} 配置, 单位为 MHz, 低 24bits 为小数部分。 | 7'h10   |

## 4.10 Reg09 Address: 0x09 Default: 0x00

| Bit | Name            | Type | Description | Default |

|-----|-----------------|------|-------------|---------|

| 7:0 | ref_freq[23:16] | R/W  | 参考 Reg08 描述 | 8'h00   |

## 4.11 Reg0A Address: 0x0A Default: 0x00

| Bit | Name           | Type | Description | Default |

|-----|----------------|------|-------------|---------|

| 7:0 | ref_freq[15:8] | R/W  | 参考 Reg08 描述 | 8'h00   |

## 4.12 Reg0B Address: 0x0B Default: 0x00

| Bit | Name          | Type | Description | Default |

|-----|---------------|------|-------------|---------|

| 7:0 | ref_freq[7:0] | R/W  | 参考 Reg08 描述 | 8'h00   |

## 4.13 Reg0C Address: 0x0C Default: 0x50

| Bit | Name            | Type | Description          | Default |

|-----|-----------------|------|----------------------|---------|

| 7:0 | tx_preamble_len | R/W  | 发射 Preamble 长度, 单位字节 | 8'h50   |

## 4.14 Reg0D Address: 0x0D Default: 0x30

| Bit | Name              | Type | Description                                                            | Default |

|-----|-------------------|------|------------------------------------------------------------------------|---------|

| 7   | payload_bit_order | R/W  | Payload bit 顺序:<br>0: LSB 低位在前<br>1: MSB 高位在前                          | 1'b0    |

| 6   | manchester_inv    | R/W  | 曼彻斯特编码:<br>0: 上升沿为编码 1, 下降沿为编码 0<br>1: 下降沿为编码 1, 上升沿为编码 0              | 1'b0    |

| 5   | syncword_en       | R/W  | Syncword 同步字使能:<br>0: Disable<br>1: Enable                             | 1'b1    |

| 4   | preamble_en       | R/W  | 设置 Preamble 前导码使能:<br>0: Disable<br>1: Enable                          | 1'b1    |

| 3:2 | pkt_enc_type      | R/W  | 数据包编码:<br>00: NRZ<br>01: 曼彻斯特编码<br>10: 无效<br>11: 交织编码                  | 2'b00   |

| 1:0 | fec_type          | R/W  | 数据包 FEC 类型:<br>00: NO FEC<br>01: 1/3 FEC<br>10: 2/3 FEC<br>11: 1/2 FEC | 2'b00   |

## 4.15 Reg0E Address: 0x0E Default: 0x32

| Bit | Name             | Type | Description                                   | Default |

|-----|------------------|------|-----------------------------------------------|---------|

| 7   | length_byte_swap | R/W  | 包长度控制域为两个字节时, 高低字节顺序:<br>0: 低字节在前<br>1: 高字节在前 | 1'b0    |

| 6   | length_sel       | R/W  | 包长度控制域字节配置:<br>0: 1 字节<br>1: 2 字节             | 1'b0    |

| Bit | Name          | Type | Description                                                                                                                                                                    | Default |

|-----|---------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 5   | crc_en        | R/W  | CRC 使能:<br>0: Disable<br>1: Enable                                                                                                                                             | 1'b1    |

| 4   | scramble_en   | R/W  | 数据白化 (扰码) 使能:<br>0: Disable<br>1: Enable                                                                                                                                       | 1'b1    |

| 3   | fifo_share_en | R/W  | FIFO 共享设置:<br>0: RX 和 TX 各 128 字节 FIFO<br>1: RX 和 TX 共用 256 字节 FIFO                                                                                                            | 1'b0    |

| 2   | direct_mode   | R/W  | 直通模式使能:<br>0: Disable<br>1: Enable                                                                                                                                             | 1'b0    |

| 1:0 | packet_mode   | R/W  | 数据包控制模式:<br>00: 模式 0, 循环发射 TX FIFO 中的数据, 需要 MCU 写命令退出接收或发射状态<br>01: 模式 1, 由寄存器控制数据包长度<br>10: 模式 2, TX FIFO 中的第一个或 2 个字节作为包长度<br>11: 模式 3, 含有 length, address, seqnum 等多种数据域的模式 | 2'b10   |

## 4.16 Reg10 Address: 0x10 Default: 0x40

| Bit | Name            | Type | Description                                            | Default |

|-----|-----------------|------|--------------------------------------------------------|---------|

| 7:4 | retx_times      | R/W  | Auto ACK 使能时, 发射端未收到 ACK 包时自动重发的次数                     | 4'h4    |

| 3   | rssi_val_sel    | R/W  | 读取 RSSI 时, 选择读取的数据内容:<br>0: 经过计算的 RSSI 值<br>1: 原始信号幅度值 | 1'b0    |

| 2   | preamble_int_en | R/W  | 接收 Preamble (前导码) 匹配中断使能:<br>0: Disable<br>1: Enable   | 1'b0    |

| 1   | syncword_int_en | R/W  | 接收 Syncword (同步字) 匹配中断使能:<br>0: Disable<br>1: Enable   | 1'b0    |

| 0   | reserved        | R/W  | -                                                      | 1'b0    |

## 4.17 Reg11 Address: 0x11 Default: 0x00

| Bit | Name         | Type | Description                                                                                                                                                              | Default |

|-----|--------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 7   | reserved     | R/W  | -                                                                                                                                                                        | 1'b0    |

| 6   | int_flag_clr | R/W  | 写‘1’清除中断标志                                                                                                                                                               | 1'b0    |

| 5   | miso_tri_opt | R/W  | SPI 在非工作状态时, spi_miso 状态:<br>0: 高阻<br>1: 输出                                                                                                                              | 1'b0    |

| 4:3 | reserved     | R/W  | -                                                                                                                                                                        | 2'b00   |

| 2:0 | brclk_sel    | R/W  | GPIO brclk 输出时钟选择:<br>000: rx_clk 接收 bit rate 时钟<br>001: xtal_clk 晶振时钟<br>010: xtal_clk/8<br>011: xtal_clk/16<br>100: 频综时钟<br>101: tx_clk 发射 bit rate 时钟<br>111: ADC_clk | 3'b000  |

## 4.18 Reg1D Address: 0x1D Default: 0x80

| Bit | Name     | Type | Description                                                    | Default |

|-----|----------|------|----------------------------------------------------------------|---------|

| 7:6 | vdddig   | R/W  | 数字 LDO 输出电压设置:<br>00: 0.8V<br>01: 1.0V<br>10: 1.2V<br>11: 1.4V | 2'b10   |

| 5:0 | reserved | R/W  | -                                                              | 6'h00   |

## 4.19 Reg20 Address: 0x20 Default: 0x50

| Bit | Name           | Type | Description                                                                                           | Default |

|-----|----------------|------|-------------------------------------------------------------------------------------------------------|---------|

| 7:6 | frequency_band | R/W  | 工作频段设置:<br>00: 800MHz~1GHz 频段<br>01: 400MHz~500MHz 频段<br>10: 267MHz~350MHz 频段<br>11: 200MHz~250MHz 频段 | 2'b01   |

| 5:0 | Reserved       | R/W  | -                                                                                                     | 6'h10   |

## 4.20 Reg21 Address: 0x21 Default: 0x60

| Bit | Name       | Type | Description                                      | Default |

|-----|------------|------|--------------------------------------------------|---------|

| 7   | reserved   | R/W  | -                                                | 1'b0    |

| 6   | pa_ramp_en | R/W  | PA RAMP 使能:<br>0: Disable<br>1: Enable           | 1'b1    |

| 5:0 | pa_bias    | R/W  | PA_bias 控制:<br>000000: 最小<br>.....<br>111111: 最大 | 6'h20   |

## 4.21 Reg27 Address: 0x27 Default: 0x60

| Bit | Name     | Type | Description                     | Default |

|-----|----------|------|---------------------------------|---------|

| 7   | reserved | R/W  | -                               | 1'b0    |

| 6   | pa_drvh  | R/W  | PA 前级驱动设置:<br>0: Low<br>1: High | 1'b1    |

| 5:0 | pa_gain  | R/W  | PA 增益控制                         | 6'h20   |

## 4.22 Reg28 Address: 0x28 Default: 0x19

| Bit | Name           | Type | Description                                                                             | Default |

|-----|----------------|------|-----------------------------------------------------------------------------------------|---------|

| 7   | rssi_Reg_clr   | R/W  | 写‘1’清除被锁定的 RSSI                                                                         | 1'b0    |

| 6   | rssi_sel       | R/W  | 收到同步字后锁定 RSSI 值:<br>0: Disable<br>1: Enable                                             | 1'b0    |

| 5   | rx_rssi_thr_en | R/W  | 接收时判断 RSSI, 如果收到前导码的 RSSI 低于设置的 RSSI 门限值 (Reg2C), 会复位解调器重新接收<br>0: Disable<br>1: Enable | 1'b0    |

| 4   | agc_en         | R/W  | AGC 使能:<br>0: Disable<br>1: Enable                                                      | 1'b1    |

| 3:0 | reserved       | R/W  | -                                                                                       | 4'h9    |

## 4.23 Reg2B Address: 0x2B Default: 0xFF

| Bit | Name      | Type | Description | Default |

|-----|-----------|------|-------------|---------|

| 7:6 | reserved  | R/W  | -           | 2'b11   |

| 5:4 | rxfe_gn   | R/W  | rxfe 增益控制   | 2'b11   |

| 3:2 | filter_gn | R/W  | Filter 增益控制 | 2'b11   |

| 1:0 | pga_gn    | R/W  | PGA 增益控制    | 2'b11   |

## 4.24 Reg2C Address: 0x2C Default: 0xFF

| Bit | Name        | Type | Description              | Default |

|-----|-------------|------|--------------------------|---------|

| 7:0 | rx_rssi_thr | R/W  | 接收 RSSI 门限值, 参考 Reg28[5] | 8'hFF   |

## 4.25 Reg2D Address: 0x2D Default: 0x10

| Bit | Name     | Type | Description                        | Default |

|-----|----------|------|------------------------------------|---------|

| 7   | cw_mode  | R/W  | 发射载波模式:<br>0: Disable<br>1: Enable | 1'b0    |

| 6:4 | reserved | R/W  | -                                  | 3'b001  |

| 3   | ook_en   | R/W  | 调制解调模式选择:<br>0: FSK<br>1: OOK      | 1'b0    |

| 2:0 | reserved | R/W  | -                                  | 3'b000  |

## 4.26 Reg30 Address: 0x30 Default: 0x80

| Bit | Name          | Type | Description                           | Default |

|-----|---------------|------|---------------------------------------|---------|

| 7   | sel_gau_o     | R/W  | 发射高斯滤波器使能:<br>0: Disable<br>1: Enable | 1'b1    |

| 6:4 | reserved      | R/W  | -                                     | 3'b000  |

| 3:0 | dev_set[11:8] | R/W  | 发射调制频偏 dev_set 的高 4 位                 | 4'h0    |

## 4.27 Reg31 Address: 0x31 Default: 0x66

| Bit | Name         | Type | Description                                                                                             | Default |

|-----|--------------|------|---------------------------------------------------------------------------------------------------------|---------|

| 7:0 | dev_set[7:0] | R/W  | 发射调制频偏<br>dev_set[11:0]={Reg30[3:0],Reg31[7:0]}<br>例: 频偏为正负 25KHz 即 0.025MHz, 则<br>dev_set = 0.025*4096 | 8'h66   |

## 4.28 Reg37 Address: 0x37 Default: 0x06

| Bit | Name      | Type | Description                                            | Default |

|-----|-----------|------|--------------------------------------------------------|---------|

| 7:0 | csrst_len | R/W  | 在补偿功能使能时, 找到信号的频谱后连续收到 Reg37*4 个前导后, 则认为找到有效的 Preamble | 8'h06   |

## 4.29 Reg38 Address: 0x38 Default: 0x91

| Bit | Name          | Type | Description                        | Default |

|-----|---------------|------|------------------------------------|---------|

| 7:5 | reserved      | R/W  | -                                  | 3'b100  |

| 4   | demod_comp_en | R/W  | 解调频偏补偿:<br>0: Disable<br>1: Enable | 1'b1    |

| 3:0 | reserved      | R/W  | -                                  | 4'h1    |

## 4.30 Reg4D Address: 0x4D Default: 0x10

| Bit | Name        | Type | Description                                    | Default |

|-----|-------------|------|------------------------------------------------|---------|

| 7   | nirq_dir    | R/W  | nIRQ_flag IO 口方向:<br>0: Output<br>1: Input     | 1'b0    |

| 6   | gpio_dir[0] | R/W  | gpio[0] 方向:<br>0: Output<br>1: Input           | 1'b0    |

| 5   | gpio_dir[1] | R/W  | gpio[1] 方向:<br>0: Output<br>1: Input           | 1'b0    |

| 4   | gpio_dir[2] | R/W  | gpio[2] 方向, 默认复位输入功能:<br>0: Output<br>1: Input | 1'b1    |

| Bit | Name     | Type | Description                                                                                                                                                                                                                                                                                                                                                 | Default |

|-----|----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 3:0 | nirq_sel | R/W  | nIRQ 引脚输出功能选择:<br>0x00: pkt_flag(包括数据包完成中断<br>pkt_int, 接收前导码中断 preamble_int,<br>接收同步字中断 syncword_int)<br>0x01: pkt_int<br>0x02: preamble_int<br>0x03: syncword_int<br>0x04: fifo_flag<br>0x05: brclk (参考 Reg11[2:0]描述)<br>0x06: rxdata<br>0x07: txdata<br>0x08: tr_switch<br>0x09: tr_switch 反向<br>0x0A: rxdata<br>0x0B: txdata<br>0x0D: 高电平<br>Others: 低电平 | 4'h0    |

### 4.31 Reg4E Address: 0x4E Default: 0x45

| Bit | Name       | Type | Description                    | Default |

|-----|------------|------|--------------------------------|---------|

| 7:4 | gpio_0_sel | R/W  | gpio[0]输出功能选择, 参考 Reg4D[3:0]描述 | 4'h4    |

| 3:0 | gpio_1_sel | R/W  | gpio[1]输出功能选择, 参考 Reg4D[3:0]描述 | 4'h5    |

### 4.32 Reg4F Address: 0x4F Default: 0x67

| Bit | Name       | Type | Description                    | Default |

|-----|------------|------|--------------------------------|---------|

| 7:4 | gpio_2_sel | R/W  | gpio[2]输出功能选择, 参考 Reg4D[3:0]描述 | 4'h6    |

| 3:0 | reserved   | R/W  | -                              | 4'h7    |

### 4.33 Reg50 Address: 0x50 Default: 0x00

| Bit | Name           | Type | Description              | Default |

|-----|----------------|------|--------------------------|---------|

| 7:0 | rx_fifo_wr_ptr | R/W  | RX FIFO 写指针, 写 0x80 清除指针 | 8'h00   |

### 4.34 Reg51 Address: 0x51 Default: 0x00

| Bit | Name           | Type | Description              | Default |

|-----|----------------|------|--------------------------|---------|

| 7:0 | rx_fifo_rd_ptr | R/W  | RX FIFO 读指针, 写 0x80 清除指针 | 8'h00   |

### 4.35 Reg52 Address: 0x52 Default: 0x00

| Bit | Name         | Type | Description | Default |

|-----|--------------|------|-------------|---------|

| 7:0 | rx_fifo_data | R/W  | RX FIFO     | 8'h00   |

### 4.36 Reg53 Address: 0x53 Default: 0x00

| Bit | Name           | Type | Description              | Default |

|-----|----------------|------|--------------------------|---------|

| 7:0 | tx_fifo_wr_ptr | R/W  | TX FIFO 写指针, 写 0x80 清除指针 | 8'h00   |

### 4.37 Reg54 Address: 0x54 Default: 0x00

| Bit | Name           | Type | Description              | Default |

|-----|----------------|------|--------------------------|---------|

| 7:0 | tx_fifo_rd_ptr | R/W  | TX FIFO 读指针, 写 0x80 清除指针 | 8'h00   |

### 4.38 Reg55 Address: 0x55 Default: 0x00

| Bit | Name         | Type | Description | Default |

|-----|--------------|------|-------------|---------|

| 7:0 | tx_fifo_data | R/W  | TX FIFO     | 8'h00   |

### 4.39 Reg56 Address: 0x56 Default: 0xB7

| Bit | Name       | Type | Description    | Default |

|-----|------------|------|----------------|---------|

| 7:0 | delta_rssi | R/W  | 计算 RSSI 时的预偏移量 | 8'hB7   |

### 4.40 Reg57 Address: 0x57 Default: 0x00

| Bit | Name       | Type | Description                                                                          | Default |

|-----|------------|------|--------------------------------------------------------------------------------------|---------|

| 7:3 | reserved   | R/W  | -                                                                                    | 5'h00   |

| 2   | spi_3w_sel | R/W  | 三线 SPI 选择:<br>0: 4 线标准 SPI<br>1: 3 线 SPI, 数据线只使用 SPI_MOSI                            | 1'b0    |

| 1   | crc_err_st | R/W  | 接收 CRC 错误时, 数据包的处理方法:<br>0: 正常完成该包的接收, 退出接收状态发出数据包中断和错误 CRC 标志<br>1: 丢弃该包数据并重新进入接收状态 | 1'b0    |

| 0   | reserved   | R/W  | -                                                                                    | 1'b0    |

### 4.41 Reg58 Address: 0x58 Default: 0x00

| Bit | Name               | Type | Description                                                           | Default |

|-----|--------------------|------|-----------------------------------------------------------------------|---------|

| 7:5 | reserved           | R/W  | -                                                                     | 3'b000  |

| 4:3 | direct_tx_data_sel | R/W  | Direct mode 时, TX 数据源选择:<br>00: nIRQ 引脚<br>01: gpio[0]<br>1x: gpio[1] | 2'b00   |

| 2:0 | reserved           | R/W  | -                                                                     | 3'b000  |

## 4.42 Reg5D Address: 0x5D Default: 0x00

| Bit | Name       | Type | Description                                    | Default |

|-----|------------|------|------------------------------------------------|---------|

| 7   | nrst_sel   | R/W  | nRST 引脚功能设置:<br>0: nRST<br>1: GPIO2            | 1'b0    |

| 6   | pull_up_en | R/W  | nRST 引脚 Pull-UP 使能:<br>0: Enable<br>1: Disable | 1'b0    |

| 5:0 | reseved    | R/W  | -                                              | 5'h00   |

## 4.43 Reg60 Address: 0x60 Default: 0x80

| Bit | Name    | Type | Description                                                                                                                                         | Default |

|-----|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 7:0 | command | R/W  | 0x80: IDLE command<br>0x40: TX Command<br>0x20: RX command<br>0x05: StandBy command<br>0x06: Reset command, 需要先使能 RegA3[7]<br>0x10: FS command 打开频综 | 8'h80   |

## 4.44 Reg61 Address: 0x61 Default: 0x00

| Bit | Name         | Type | Description     | Default |

|-----|--------------|------|-----------------|---------|

| 7   | syncword_rec | R    | 接收到正确的 Syncword | 1'b0    |

| 6   | preamble_rec | R    | 接收到有效的 Preamble | 1'b0    |

| 5   | crc_error    | R    | 高电平时表示 CRC 校验错误 | 1'b0    |

| 4   | pkt_flag     | R    | pkt_flag        | 1'b0    |

| 3   | fifo_flag    | R    | fifo_flag       | 1'b0    |

| 2:0 | reserved     | R    | -               | 3'b000  |

#### 4.45 Reg64 Address: 0x64 Default: 0x00

| Bit | Name | Type | Description       | Default |

|-----|------|------|-------------------|---------|

| 7:0 | rssi | R    | 读出的值为实际 RSSI 的绝对值 | 8'h00   |

#### 4.46 Reg67 Address: 0x67 Default: 0x80

| Bit | Name    | Type | Description | Default |

|-----|---------|------|-------------|---------|

| 7   | st_idle | R    | IDLE 状态     | 1'b1    |

| 6   | st_tx   | R    | 发射状态        | 1'b0    |

| 5   | st_rx   | R    | 接收状态        | 1'b0    |

| 4   | st_fson | R    | 频综开启状态      | 1'b0    |

| 3:0 | reseved | R    | -           | 4'h0    |

#### 4.47 Reg68 Address: 0x68 Default: 0x00

| Bit | Name            | Type | Description                | Default |

|-----|-----------------|------|----------------------------|---------|

| 7:2 | reseved         | R    | -                          | 6'h0    |

| 1   | m3_seqnum_ok    | R    | 数据包模式 3 时, 接收 seqnum 匹配正确  | 1'b0    |

| 0   | m3_addr_comp_ok | R    | 数据包模式 3 时, 接收 address 匹配正确 | 1'b0    |

#### 4.48 Reg69 Address: 0x69 Default: 0x00

| Bit | Name             | Type | Description           | Default |

|-----|------------------|------|-----------------------|---------|

| 7:0 | m3_rx_fcs2_value | R    | 数据包模式 3 时, 接收 FCS2 数据 | 8'h00   |

## 4.49 Reg6A Address: 0x6A Default: 0x00

| Bit | Name                   | Type | Description             | Default |

|-----|------------------------|------|-------------------------|---------|

| 7:0 | m3_rx_payload_len[7:0] | R    | 数据包模式 3 时, 接收 length 数据 | 8'h00   |

## 4.50 Reg6B Address: 0x6B Default: 0x00

| Bit | Name                    | Type | Description             | Default |

|-----|-------------------------|------|-------------------------|---------|

| 7:0 | m3_rx_payload_len[15:8] | R    | 数据包模式 3 时, 接收 length 数据 | 8'h00   |

## 4.51 Reg6C Address: 0x6C Default: 0x00

| Bit | Name            | Type | Description           | Default |

|-----|-----------------|------|-----------------------|---------|

| 7:0 | m3_rx_addr[7:0] | R    | 数据包模式 3 时, 接收 address | 8'h00   |

## 4.52 Reg6D Address: 0x6D Default: 0x00

| Bit | Name             | Type | Description           | Default |

|-----|------------------|------|-----------------------|---------|

| 7:0 | m3_rx_addr[15:8] | R    | 数据包模式 3 时, 接收 address | 8'h00   |

## 4.53 Reg6E Address: 0x6E Default: 0x00

| Bit | Name              | Type | Description           | Default |

|-----|-------------------|------|-----------------------|---------|

| 7:0 | m3_rx_addr[23:16] | R    | 数据包模式 3 时, 接收 address | 8'h00   |

## 4.54 Reg6F Address: 0x6F Default: 0x00

| Bit | Name              | Type | Description        | Default |

|-----|-------------------|------|--------------------|---------|

| 7:0 | m3_rx_addr[31:24] | R    | 数据包模式 3 时, 接收地址域数据 | 8'h00   |

## 4.55 Reg70 Address: 0x70 Default: 0xFF

| Bit | Name                   | Type | Description   | Default |

|-----|------------------------|------|---------------|---------|

| 7:0 | scramble_init_val[7:0] | R/W  | scramble 初始化值 | 8'hFF   |

## 4.56 Reg71 Address: 0x71 Default: 0x09

| Bit | Name                 | Type | Description                       | Default |

|-----|----------------------|------|-----------------------------------|---------|

| 7   | reserved             | R/W  | -                                 | 1'b0    |

| 6   | srcamble_len         | R/W  | 伪随机数长度选择:<br>0: PN9<br>1: PN7     | 1'b0    |

| 5   | scramble_msb         | R/W  | 选择首先输出的移位寄存器:<br>0: LSB<br>1: MSB | 1'b0    |

| 4   | scramble_type        | R/W  | 伪随机数产生器类型:<br>0: 抽出模式<br>1: 插入模式  | 1'b0    |

| 3:1 | scramble_poly        | R/W  | 反馈抽头选择                            | 3'b100  |

| 0   | scramble_init_val[8] | R/W  | scramble 初始化值最高位                  | 1'b1    |

## 4.57 Reg72 Address: 0x72 Default: 0x01

| Bit | Name       | Type | Description  | Default |

|-----|------------|------|--------------|---------|

| 7:5 | reserved   | R/W  | -            | 3'b000  |

| 4:0 | sync_thres | R/W  | 同步字检测允许的错误位数 | 5'h01   |

## 4.58 Reg73 Address: 0x73 Default: 0x55

| Bit | Name         | Type | Description  | Default |

|-----|--------------|------|--------------|---------|

| 7:0 | preamble_val | R/W  | 发射前导码时的使用的数据 | 8'h55   |

## 4.59 Reg74 Address: 0x74 Default: 0x03

| Bit | Name           | Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Default |

|-----|----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 7   | auto_ack       | R/W  | auto_ack 使能:<br>0: Disable<br>1: Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1'b0    |

| 6   | ack_payload_en | R/W  | 发射 ACK 时带 payload 数据返回:<br>0: Disable<br>1: Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1'b0    |

| 5   | cont_rx_en     | R/W  | 控制接收状态机:<br>0: 接收完成数据包后退出接收状态进入 IDLE 状态<br>1: 接收完成数据包后重新再次进入接收状态                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1'b0    |

| 4   | sync_man_en    | R/W  | 同步字曼彻斯特编码使能:<br>0: Disable<br>1: Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1'b0    |

| 3   | sync_bit_order | R/W  | 同步字 bit 顺序:<br>0: 字节低位<br>1: 字节高位 MSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1'b0    |

| 2:0 | sync_len       | R/W  | 同步字长度:<br>000: {sync_id_1}<br>001: {sync_id_1, sync_id_2}<br>010: {sync_id_1, sync_id_2, sync_id_3}<br>011: {sync_id_1, sync_id_2, sync_id_3, sync_id_4}<br>100: {sync_id_1, sync_id_2, sync_id_3, sync_id_4,<br>sync_id_5}<br>101: {sync_id_1, sync_id_2, sync_id_3, sync_id_4,<br>sync_id_5, sync_id_6}<br>110: {sync_id_1, sync_id_2, sync_id_3, sync_id_4,<br>sync_id_5, sync_id_6, sync_id_7}<br>111: {sync_id_1, sync_id_2, sync_id_3, sync_id_4,<br>sync_id_5, sync_id_6, sync_id_7, sync_id_8} | 3'b011  |

## 4.60 Reg75 Address: 0x75 Default: 0xA7

| Bit | Name      | Type | Description | Default |

|-----|-----------|------|-------------|---------|

| 7:0 | sync_id_1 | R/W  | 同步字字节 1     | 8'hA7   |

## 4.61 Reg76 Address: 0x76 Default: 0xA7

| Bit | Name      | Type | Description | Default |

|-----|-----------|------|-------------|---------|

| 7:0 | sync_id_2 | R/W  | 同步字字节 2     | 8'hA7   |

## 4.62 Reg77 Address: 0x77 Default: 0x98

| Bit | Name      | Type | Description | Default |

|-----|-----------|------|-------------|---------|

| 7:0 | sync_id_3 | R/W  | 同步字字节 3     | 8'h98   |

## 4.63 Reg78 Address: 0x78 Default: 0xF3

| Bit | Name      | Type | Description | Default |

|-----|-----------|------|-------------|---------|

| 7:0 | sync_id_4 | R/W  | 同步字字节 4     | 8'hF3   |

## 4.64 Reg79 Address: 0x79 Default: 0x98

| Bit | Name      | Type | Description | Default |

|-----|-----------|------|-------------|---------|

| 7:0 | sync_id_5 | R/W  | 同步字字节 5     | 8'h98   |

## 4.65 Reg7A Address: 0x7A Default: 0xF3

| Bit | Name      | Type | Description | Default |

|-----|-----------|------|-------------|---------|

| 7:0 | sync_id_6 | R/W  | 同步字字节 6     | 8'hF3   |

## 4.66 Reg7B Address: 0x7B Default: 0x98

| Bit | Name      | Type | Description | Default |

|-----|-----------|------|-------------|---------|

| 7:0 | sync_id_7 | R/W  | 同步字字节 7     | 8'h98   |

## 4.67 Reg7C Address: 0x7C Default: 0xF3

| Bit | Name      | Type | Description | Default |

|-----|-----------|------|-------------|---------|

| 7:0 | sync_id_8 | R/W  | 同步字字节 8     | 8'hF3   |

## 4.68 Reg7D Address: 0x7D Default: 0x0E

| Bit | Name             | Type | Description                      | Default |

|-----|------------------|------|----------------------------------|---------|

| 7:0 | payload_len[7:0] | R/W  | payload 长度, 在数据包模式 1 和数据包模式 3 有效 | 8'h0E   |

## 4.69 Reg7E Address: 0x7E Default: 0x00

| Bit | Name              | Type | Description                      | Default |

|-----|-------------------|------|----------------------------------|---------|

| 7:0 | payload_len[15:8] | R/W  | payload 长度, 在数据包模式 1 和数据包模式 3 有效 | 8'h00   |

## 4.70 Reg7F Address: 0x7F Default: 0x00

| Bit | Name     | Type | Description                                 | Default |

|-----|----------|------|---------------------------------------------|---------|

| 7:1 | reserved | R/W  | -                                           | 7'h0    |

| 0   | page_sel | R/W  | 寄存器页地址:<br>0: Reg00~Reg7E<br>1: Reg80~RegFE | 1'b0    |

## 4.71 Reg80 Address: 0x80 Default: 0x1D

| Bit | Name             | Type | Description                                                                                                                                        | Default |

|-----|------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 7:6 | reserved         | R/W  | -                                                                                                                                                  | 2'b00   |

| 5   | m3_length_en     | R/W  | 数据包模式 3 时, 数据长度域控制:<br>0: Disable<br>1: Enable                                                                                                     | 1'b0    |

| 4   | m3_crc_sel       | R/W  | 数据包模式 3 时, CRC 的校验范围:<br>0: All payload<br>1: 仅 FIFO 中的数据                                                                                          | 1'b1    |

| 3:0 | m3_ack_node_ctrl | R/W  | 数据包模式 3 且 AUTO_ACK 功能开启, 返回的 ACK 包控制:<br>[3]: 为‘1’时使能返回接收到的数据长度<br>[2]: 为‘1’时使能返回接收到的地址<br>[1]: 为‘1’时使能返回接收到的 seqnum<br>[0]: 为‘1’时使能返回接收到的 FCS2 数据 | 4'hD    |

## 4.72 Reg81 Address: 0x81 Default: 0x78

| Bit | Name               | Type | Description                                                               | Default |

|-----|--------------------|------|---------------------------------------------------------------------------|---------|

| 7:6 | reserved           | R/W  | -                                                                         | 2'b01   |

| 5:4 | m3_addr_size       | R/W  | 数据包模式 3 时, 地址长度:<br>00: 1 字节<br>01: 2 字节<br>10: 3 字节<br>11: 4 字节          | 2'b11   |

| 3   | reserved           | R/W  | -                                                                         | 1'b1    |

| 2   | m3_addr_split_mode | R/W  | 数据包模式 3 时, 将地址分为源地址和目的地址, 在返回 ACK 时, 将收到的源地址和目的地址位置互换:<br>0: 不互换<br>1: 互换 | 1'b0    |

| 1   | m3_addr_pos_sel    | R/W  | 数据包模式 3 时, 地址位置选择:<br>0: address 放在 length 之后<br>1: address 放在 length 之前  | 1'b0    |

| Bit | Name       | Type | Description                                  | Default |

|-----|------------|------|----------------------------------------------|---------|

| 0   | m3_addr_en | R/W  | 数据包模式 3 时, 地址域控制:<br>0: Disable<br>1: Enable | 1'b0    |

#### 4.73 Reg82 Address: 0x82 Default: 0x00

| Bit | Name             | Type | Description    | Default |

|-----|------------------|------|----------------|---------|

| 7:0 | m3_addr_val[7:0] | R/W  | 数据包模式 3 时, 地址值 | 8'h00   |

#### 4.74 Reg83 Address: 0x83 Default: 0x00

| Bit | Name              | Type | Description    | Default |

|-----|-------------------|------|----------------|---------|

| 7:0 | m3_addr_val[15:8] | R/W  | 数据包模式 3 时, 地址值 | 8'h00   |

#### 4.75 Reg84 Address: 0x84 Default: 0x00

| Bit | Name               | Type | Description    | Default |

|-----|--------------------|------|----------------|---------|

| 7:0 | m3_addr_val[23:16] | R/W  | 数据包模式 3 时, 地址值 | 8'h00   |

#### 4.76 Reg85 Address: 0x85 Default: 0x03

| Bit | Name               | Type | Description    | Default |

|-----|--------------------|------|----------------|---------|

| 7:0 | m3_addr_val[31:24] | R/W  | 数据包模式 3 时, 地址值 | 8'h03   |

#### 4.77 Reg86 Address: 0x86 Default: 0x33

| Bit | Name                  | Type | Description                          | Default |

|-----|-----------------------|------|--------------------------------------|---------|

| 7:0 | m3_addr_bit_mask[7:0] | R/W  | 数据包模式 3 时, 地址过滤, mask 为‘1’时对应地址位不作比较 | 8'h33   |

## 4.78 Reg87 Address: 0x87 Default: 0x33

| Bit | Name                   | Type | Description                          | Default |

|-----|------------------------|------|--------------------------------------|---------|

| 7:0 | m3_addr_bit_mask[15:8] | R/W  | 数据包模式 3 时, 地址过滤, mask 为‘1’时对应地址位不作比较 | 8'h33   |

## 4.79 Reg88 Address: 0x88 Default: 0x10

| Bit | Name                    | Type | Description                          | Default |

|-----|-------------------------|------|--------------------------------------|---------|

| 7:0 | m3_addr_bit_mask[23:16] | R/W  | 数据包模式 3 时, 地址过滤, mask 为‘1’时对应地址位不作比较 | 8'h10   |

## 4.80 Reg89 Address: 0x89 Default: 0x00

| Bit | Name                    | Type | Description                          | Default |

|-----|-------------------------|------|--------------------------------------|---------|

| 7:0 | m3_addr_bit_mask[31:24] | R/W  | 数据包模式 3 时, 地址过滤, mask 为‘1’时对应地址位不作比较 | 8'h00   |

## 4.81 Reg8A Address: 0x8A Default: 0x00

| Bit | Name               | Type | Description                                                                       | Default |

|-----|--------------------|------|-----------------------------------------------------------------------------------|---------|

| 7:6 | reserved           | R/W  | -                                                                                 | 2'b00   |

| 5   | m3_seqnum_auto_inc | R/W  | 数据包模式 3 时, seqnum 配置方式:<br>0: seqnum 数据由{Reg8c,Reg8b}配置<br>1: 由内部 seqnum 计数器自动加 1 | 1'b0    |

| 4   | m3_seqnum_en       | R/W  | 数据包模式 3 时, seqnum 数据使能:<br>0: Disable<br>1: Enable                                | 1'b0    |

| 3   | m3_seqnum_bit_size | R/W  | 数据包模式 3 时, seqnum 数据长度:<br>0: 8bits<br>1: 16bits                                  | 1'b0    |

| 2:0 | reserved           | R/W  | -                                                                                 | 3'b000  |

## 4.82 Reg8B Address: 0x8B Default: 0x00

| Bit | Name            | Type | Description         | Default |

|-----|-----------------|------|---------------------|---------|

| 7:0 | seqnum_Reg[7:0] | R/W  | 数据包模式 3 时, seqnum 值 | 8'h00   |

## 4.83 Reg8C Address: 0x8C Default: 0x50

| Bit | Name             | Type | Description         | Default |

|-----|------------------|------|---------------------|---------|

| 7:0 | seqnum_Reg[15:8] | R/W  | 数据包模式 3 时, seqnum 值 | 8'h50   |

## 4.84 Reg8D Address: 0x8D Default: 0x30

| Bit | Name       | Type | Description                                       | Default |

|-----|------------|------|---------------------------------------------------|---------|

| 7:1 | reserved   | R/W  | -                                                 | 7'h30   |

| 0   | m3_fcs2_en | R/W  | 数据包模式 3 时, FCS2 数据域使能:<br>0: Disable<br>1: Enable | 1'b0    |

## 4.85 Reg8E Address: 0x8E Default: 0x32

| Bit | Name        | Type | Description            | Default |

|-----|-------------|------|------------------------|---------|

| 7   | m3_fcs2_val | R/W  | 数据包模式 3 时, ACK request | 1'b0    |

| 6:0 | reserved    | R/W  | -                      | 7'h32   |

## 4.86 Reg94 Address: 0x94 Default: 0x08

| Bit | Name          | Type | Description                            | Default |

|-----|---------------|------|----------------------------------------|---------|

| 7:5 | reserved      | R/W  | -                                      | 3'b000  |

| 4   | crc_bit_order | R/W  | CRC bit 顺序:<br>0: LSB<br>1: MSB        | 1'b0    |

| 3   | crc_inv       | R/W  | CRC bit 取反:<br>0: Disable<br>1: Enable | 1'b1    |

| Bit | Name       | Type | Description                                            | Default |

|-----|------------|------|--------------------------------------------------------|---------|

| 2   | crc_man_en | R/W  | CRC 曼彻斯特编码使能:<br>0: Disable<br>1: Enable               | 1'b0    |

| 1:0 | crc_len    | R/W  | CRC 长度:<br>00: 8 位<br>01: 16 位<br>10: 24 位<br>11: 32 位 | 2'b00   |

#### 4.87 Reg95 Address: 0x95 Default: 0x20

| Bit | Name          | Type | Description | Default |

|-----|---------------|------|-------------|---------|

| 7:0 | crc_poly[7:0] | R/W  | CRC 多项式配置   | 8'h20   |

#### 4.88 Reg96 Address: 0x96 Default: 0x26

| Bit | Name           | Type | Description | Default |

|-----|----------------|------|-------------|---------|

| 7:0 | crc_poly[15:8] | R/W  | CRC 多项式配置   | 8'h26   |

#### 4.89 Reg97 Address: 0x97 Default: 0x1F

| Bit | Name            | Type | Description | Default |

|-----|-----------------|------|-------------|---------|

| 7:0 | crc_poly[23:16] | R/W  | CRC 多项式配置   | 8'h1F   |

#### 4.90 Reg98 Address: 0x98 Default: 0x68

| Bit | Name            | Type | Description | Default |

|-----|-----------------|------|-------------|---------|

| 7:0 | crc_poly[31:24] | R/W  | CRC 多项式配置   | 8'h68   |

## 4.91 Reg99 Address: 0x99 Default: 0x04

| Bit | Name              | Type | Description   | Default |

|-----|-------------------|------|---------------|---------|

| 7:0 | crc_init_val[7:0] | R/W  | CRC 移位寄存器初始化值 | 8'h04   |

## 4.92 Reg9A Address: 0x9A Default: 0xAE

| Bit | Name               | Type | Description   | Default |

|-----|--------------------|------|---------------|---------|

| 7:0 | crc_init_val[15:8] | R/W  | CRC 移位寄存器初始化值 | 8'hAE   |

## 4.93 Reg9B Address: 0x9B Default: 0x89

| Bit | Name                | Type | Description   | Default |

|-----|---------------------|------|---------------|---------|

| 7:0 | crc_init_val[23:16] | R/W  | CRC 移位寄存器初始化值 | 8'h89   |

## 4.94 Reg9C Address: 0x9C Default: 0x84

| Bit | Name                | Type | Description   | Default |

|-----|---------------------|------|---------------|---------|

| 7:0 | crc_init_val[31:24] | R/W  | CRC 移位寄存器初始化值 | 8'h84   |

## 4.95 Reg9D Address: 0x9D Default: 0x03

| Bit | Name             | Type | Description                              | Default |

|-----|------------------|------|------------------------------------------|---------|

| 7   | tx_data_inv      | R/W  | 发射 bit 数据取反                              | 1'b0    |

| 6   | rx_data_inv      | R/W  | 解调器输出的 bit 数据取反                          | 1'b0    |

| 5   | auto_det_tx_chl  | R/W  | 发射前检测信道 RSSI:<br>0: Disable<br>1: Enable | 1'b0    |

| 4   | auto_det_tx_mode | R/W  | 发射检测信道模式:<br>0: 检测次数满且信道仍然忙, 退出          | 1'b0    |

| Bit | Name           | Type | Description                       | Default |

|-----|----------------|------|-----------------------------------|---------|

|     |                |      | 发射模式, 发射数据失败<br>1: 持续检测, 直到发射数据成功 |         |

| 3:0 | auto_det_times | R/W  | 发射前最大检测信道次数                       | 4'h3    |

## 4.96 Reg9E Address: 0x9E Default: 0x80

| Bit | Name         | Type | Description | Default |

|-----|--------------|------|-------------|---------|

| 7:0 | chl_busy_thr | R/W  | 发射前检测信道门限值  | 8'h80   |

## 4.97 Reg9F Address: 0x9F Default: 0x26

| Bit | Name           | Type | Description                               | Default |

|-----|----------------|------|-------------------------------------------|---------|

| 7:6 | reserved       | R/W  | -                                         | 2'b00   |

| 5:0 | fifo_empty_thr | R/W  | TX FIFO 空门限, FIFO 数据低于门限值时 fifo_flag 置‘1’ | 6'h26   |

## 4.98 RegA0 Address: 0xA0 Default: 0x50

| Bit | Name          | Type | Description                                  | Default |

|-----|---------------|------|----------------------------------------------|---------|

| 7:6 | reserved      | R/W  | -                                            | 2'b00   |

| 5:0 | fifo_full_thr | R/W  | RX FIFO 满门限, RX FIFO 数据高于门限值时 fifo_flag 置‘1’ | 6'h50   |

## 4.99 RegA3 Address: 0xA3 Default: 0x42

| Bit | Name            | Type | Description                                  | Default |

|-----|-----------------|------|----------------------------------------------|---------|

| 7   | srst_cmd_enable | R/W  | Reset Command 使能:<br>0: Disable<br>1: Enable | 1'b0    |

| Bit | Name               | Type | Description                                      | Default |

|-----|--------------------|------|--------------------------------------------------|---------|

| 6   | reserved           | R/W  | -                                                | 1'b1    |

| 5:0 | auto_ack_wait_time | R/W  | auto ack 功能开启时, 发射端发完数据包后等待 ACK 数据的时间, 超时会重新发射数据 | 6'h02   |

#### 4.100 RegE0 Address: 0xE0 Default: 0x80

| Bit | Name               | Type | Description             | Default |

|-----|--------------------|------|-------------------------|---------|

| 7:0 | rx_seqnum_val[7:0] | R    | 数据包模式 3 时, 接收 seqnum 数据 | 8'h80   |

#### 4.101 RegE1 Address: 0xE1 Default: 0x00

| Bit | Name                | Type | Description             | Default |

|-----|---------------------|------|-------------------------|---------|

| 7:0 | rx_seqnum_val[15:8] | R    | 数据包模式 3 时, 接收 seqnum 数据 | 8'h00   |

#### 4.102 RegE2 Address: 0xE2 Default: 0x01

| Bit | Name            | Type | Description | Default |

|-----|-----------------|------|-------------|---------|

| 7:0 | seqnum_cnt[7:0] | R    | seqnum_cnt  | 8'h01   |

#### 4.103 RegE3 Address: 0xE3 Default: 0x40

| Bit | Name             | Type | Description | Default |

|-----|------------------|------|-------------|---------|

| 7:0 | seqnum_cnt[15:8] | R    | seqnum_cnt  | 8'h40   |

# 5 功能描述

UM2010 是一款高集成度的 sub-1GHz 无线收发机。支持 OOK、2-(G)FSK 调制解调方式，支持 Direct 和 Packet 数据处理模式，支持标准四线 SPI 和自定义三线 SPI 接口。

## 5.1 接收机

芯片内部集成了低功耗、高性能的低中频架构接收机。天线接收到的射频信号经过低噪声放大器放大之后，由正交混频器下变频至中频。I/Q 两路中频信号进一步通过低通滤波器（LPF）、可编程放大器（PGA）放大到合适的幅度，然后由 ADC 转换到数字域。

接收到的信号在数字域完成镜像抑制、中频滤波、基带滤波和 OOK/(G)FSK 解调。解调后的数据在直通模式下可以通过 GPIO 管脚直接输出，也可以在包模式下通过 SPI 从内部 FIFO 中读取。

## 5.2 发射机

芯片发射机采用基于频率综合器的单点调制结构。内部的高效率功率放大器可以输出最大 +18dBm 的功率，输出功率可以在-20dBm 至+18dBm 范围内调节，调节精度为 1dB。在 GFSK 模式下，发射数据经过高斯滤波之后再送入频率综合器进行调制，使得发射频谱更为集中。为了降低 PA 开关过程中引起的频谱杂散和毛刺，并削弱对 VCO 的牵引，PA 的输出功率引入了缓慢升降机制（PA Ramp）。

发射机支持包模式和直通模式。包模式下，数据先填入内部的 FIFO，芯片会自动按照配置完成相应的包处理然后由发射机发射出去。直通模式下，发射数据可以通过 GPIO 直接输入并发射出去。

## 5.3 系统复位

芯片内部集成了上电复位 (POR)、外部复位和软件复位。上电默认状态下，GPIO2 默认为外部复位信号(nRST)输入，只要 nRST 拉低就可以完成对芯片的复位。此外，还可以通过 SPI 写命令的方式对芯片进行复位操作。芯片一旦复位，内部所有配置都恢复到上电默认状态，MCU 需要对芯片重新进入初始化操作。

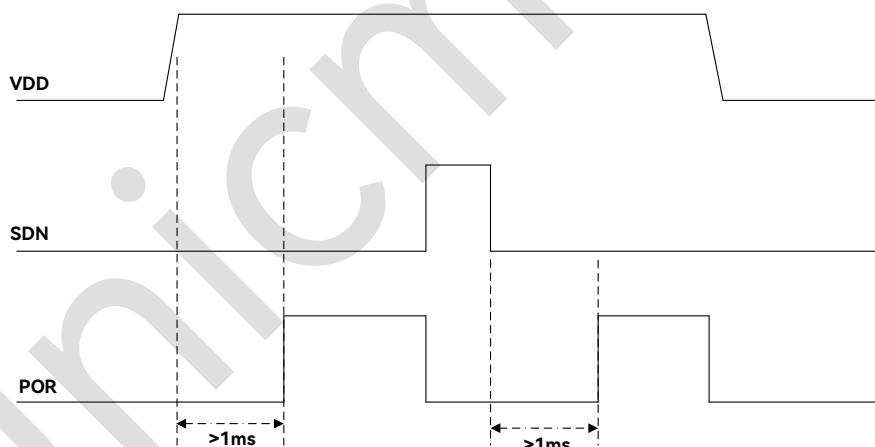

### 5.3.1 POR 复位

芯片上电或者退出全局关断模式 (SDN 拉低) 后，芯片会触发上电复位 (POR)，复位之后芯片默认处于 IDLE 状态。上电稳定或 SDN 拉低后，至少等待 4.5ms 的时间等待晶体启动稳定后，再进行 SPI 操作。

图 5-1: POR 复位时序图

### 5.3.2 外部复位

芯片上电 GPIO2 默认配置为外部 nRST 复位功能，通过拉低 nRST 引脚电平使芯片处于复位状态，拉高 nRST 引脚电平使芯片处于工作状态。如果 GPIO2 配置为其他功能，需要先关闭 GPIO2 的复位功能，否则可能存在配置过程中使芯片复位。芯片外部复位后，内部所有配置都恢复到默认状态，需要重新进行配置。

表 5-1：外部复位相关寄存器

| 寄存器地址 | 位数 | R/W | 比特名        | 功能说明                                           |

|-------|----|-----|------------|------------------------------------------------|

| 0x5D  | 7  | R/W | nrst_sel   | nRST 引脚功能设置：<br>0: nRST<br>1: GPIO2            |

|       | 6  | R/W | pull_up_en | nRST 引脚 Pull-UP 使能：<br>0: Enable<br>1: Disable |

### 5.3.3 软件复位

软件复位是通过 SPI 写命令的方式对芯片进行软复位操作，芯片除了 Shutdown 和 Sleep 状态外的所有状态，都可以通过 SPI 写命令进行软复位操作，写复位命令前需要先使能软件复位。软复位是复位整个数字系统，包括 SPI 接口、寄存器、FIFO、数字内核。芯片复位后回到 IDLE 状态，所有寄存器丢失，需要重新初始化系统。软复位流程如下：

1. SPI 写指令，RegA3=0xC2，使能复位命令。

2. SPI 写指令，Reg60=0x06，写复位命令进行复位。

表 5-2：软复位相关寄存器

| 寄存器地址 | 位数  | R/W | 比特名             | 功能说明                                         |

|-------|-----|-----|-----------------|----------------------------------------------|

| 0x60  | 7:0 | R/W | command         | 0x06: Reset command                          |

| 0xA3  | 7   | R/W | srst_cmd_enable | Reset Command 使能：<br>0: Disable<br>1: Enable |

## 5.4 频率综合器

芯片内部集成了高精度的 Sigma-Delta 小数分频频率综合器，在 200MHz~960MHz 范围内产生精准的载波频率。载波频率可以通过两种方式进行设置：

1. 寄存器直接设置：在这种方式下，把所需的载波频率值直接写入相应的寄存器即可。

2. 查表方式。在这种方式下，可以按照以下公式进行频率设置：

$$F_c = F_0 + N \cdot F_{step}$$

其中,  $F_0$ 、N 和  $F_{step}$  都可以通过寄存器进行设置。

- $F_0$  由{Reg00[6:0],Reg01,Reg02,Reg03}共 31bits 位设置, 高 11 位表示整数, 低 20 位表示小数, 单位为 MHz。

- N 为整数由 Reg04 设置。

- $F_{step}$  由{Reg05,Reg06,Reg07}设置, 低 20 位为小数, 单位为 MHz。

如设置  $F_c=433.92\text{MHz}$ , 可以设置  $F_0 = 433.92$ ,  $N = 0$ ,  $F_{step} = 0$ 。即写入以下寄存器值:

Reg00=0x1B

Reg01=0x1E

Reg02=0xB8

Reg03=0x51

Reg04=0x00

Reg05=0x00

Reg06=0x00

Reg07=0x00

表 5-3: 频率综合器相关寄存器

| 寄存器地址 | 位数  | R/W | 比特名           | 功能说明                                                                                                                                                                                                                                   |

|-------|-----|-----|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x00  | 6:0 | R/W | rf_f0[30:24]  | 信道频率 $f_0[30:24]$ 。<br>信道频率 $rf\_freq$ 设置公式:<br>$rf\_freq=rf\_f0+ch\_num*f\_step$<br>$rf\_f0$ 由{Reg00,Reg01,Reg02,Reg03}配置, 单位为 MHz, 低 20 位为小数;<br>$ch\_num$ 由 Reg04 配置;<br>步进频率 $f\_step$ 由{Reg05,Reg06,Reg07}配置, 单位为 MHz, 低 20 位为小数。 |

| 0x01  | 7:0 | R/W | rf_f0[23:16]  | 信道频率 $f_0[23:16]$                                                                                                                                                                                                                      |

| 0x02  | 7:0 | R/W | rf_f0[15:8]   | 信道频率 $f_0[15:8]$                                                                                                                                                                                                                       |

| 0x03  | 7:0 | R/W | rf_f0[7:0]    | 信道频率 $f_0[7:0]$                                                                                                                                                                                                                        |

| 0x04  | 7:0 | R/W | ch_num        | 信道号 $ch\_num$ , 参考 Reg00 描述                                                                                                                                                                                                            |

| 0x05  | 7:0 | R/W | f_step[23:16] | 信道步进频率 $f\_step[23:16]$ , 单位为 MHz, 低 20 位为小数, 参考 Reg00 描述                                                                                                                                                                              |

| 0x06  | 7:0 | R/W | f_step[15:8]  | 信道步进频率 $f\_step[15:8]$ , 参考 Reg00 描述                                                                                                                                                                                                   |

| 寄存器地址 | 位数  | R/W | 比特名            | 功能说明                                                                                                  |

|-------|-----|-----|----------------|-------------------------------------------------------------------------------------------------------|

| 0x07  | 7:0 | R/W | f_step[7:0]    | 信道步进频率 f_step[7:0], 参考 Reg00 描述                                                                       |

| 0x20  | 7:6 | R/W | frequency_band | 工作频段设置:<br>00: 800MHz~1GHz 频段<br>01: 400MHz~500MHz 频段<br>10: 267MHz~350MHz 频段<br>11: 200MHz~250MHz 频段 |

## 5.5 晶体振荡器

晶体振荡器用于为锁相环提供基准时钟, 为数字模块提供系统时钟。负载电容取决于晶体指定  $C_L$  参数。XI 与 XO 之间的总的负载电容应该等于  $C_L$ , 以使晶体准确振荡在参考值范围内。

$$C_L = \frac{1}{\frac{1}{C1} + \frac{1}{C2}} + C_{PCB} + C_{IC}$$

$C1$  和  $C2$  分别为晶体两端挂的负载匹配电容,  $C_{PCB}$  为 PCB 寄生引入的等效电容 (约 0.5pF)。

$C_{IC}$  为芯片 XI 和 XO 管脚引入的等效电容 (约 2.5pF)。晶体的等效串联电阻应在指定规格之内, 以保证晶体能可靠起振。也可以用一个外部信号源连接至 XI 管脚来取代传统的晶体。外部时钟信号的峰峰值在 300mV 到 700mV 之间, 并通过隔直电容耦合到 XI 管脚。晶体的精度越高, 接收性能越好。UM2010 推荐使用负载电容 ( $CL$ ) 为 20pF, 精度为 10ppm 的 26MHz 晶体, 板级外挂的负载匹配电容  $C1$  和  $C2$  的容值约 20pF。

芯片发射和接收的频点可以通过调整负载匹配电容和软件修正频点, 软件修正通过寄存器 Reg08/Reg09/Reg0A/Reg0B, 其中低 24 位为小数。

表 5-4: 晶振相关寄存器

| 寄存器地址 | 位数  | R/W | 比特名             | 功能说明                                                                                |

|-------|-----|-----|-----------------|-------------------------------------------------------------------------------------|

| 0x08  | 6:0 | R/W | ref_freq[30:24] | 参考频率 (晶振频率) 设置, ref_freq 由 {Reg08[6:0],Reg09,Reg0A,Reg0B} 配置, 单位为 MHz, 低 24 位为小数部分。 |

| 0x09  | 7:0 | R/W | ref_freq[23:16] | 参考 Reg08 描述                                                                         |

| 0x0A  | 7:0 | R/W | ref_freq[15:8]  | 参考 Reg08 描述                                                                         |

| 0x0B  | 7:0 | R/W | ref_freq[7:0]   | 参考 Reg08 描述                                                                         |

## 5.6 AGC

芯片的接收通路集成了 AGC 功能，Mixer、LPF、PGA 的增益受 AGC 环路调节。AGC 的环路控制在数字域完成，通过设定合理的 AGC 控制参数，芯片接收机的灵敏度、选择性和线性度可以达到最佳的性能。

表 5-5: AGC 相关寄存器

| 寄存器地址 | 位数 | R/W | 比特名    | 功能说明                               |

|-------|----|-----|--------|------------------------------------|

| 0x28  | 4  | R/W | agc_en | AGC 使能:<br>0: Disable<br>1: Enable |

## 5.7 RSSI

芯片内部集成的输入信号强度指示 (RSSI) 功能可以对天线端接收到的信号强度进行评估。RSSI 检测必须在 RX 状态下进行，检测到的是信道内的信号强度。

UM2010 内置信号检测模块，用于接收数据包时测量 ADC 的数据信号强度 RSSI\_RAW，在 AGC (自动增益控制) 使能时，使用 RSSI\_RAW 值对接收链路增益自动调节，同时可自动计算出 RF 输入端的 RSSI (信号强度指示) 值；也可以使用 RSSI\_RAW 值手动调节 (AGC 关闭) 接收链路增益，并根据增益值自行计算 RSSI。RSSI\_RAW 值或自动计算的 RSSI 值可以从寄存器 Reg64 读取。

表 5-6: RSSI 相关寄存器列表

| 寄存器地址 | 位数 | R/W | 比特名            | 功能说明                                                        |

|-------|----|-----|----------------|-------------------------------------------------------------|

| 0x10  | 3  | R/W | rssi_val_sel   | 读取 RSSI 时，选择读取的数据内容：<br>0: 经过计算的 RSSI 值<br>1: 原始信号幅度值       |

| 0x28  | 7  | R/W | rssi_Reg_clr   | 写‘1’清除被锁定的 RSSI                                             |

|       | 6  | R/W | rssi_sel       | 收到同步字后锁定 RSSI 值：<br>0: Disable<br>1: Enable                 |

|       | 5  | R/W | rx_rssi_thr_en | 接收时判断 RSSI，如果收到前导码的 RSSI 低于设置的 RSSI 门限值 (Reg2C)，会复位解调器重新接收： |

| 寄存器地址 | 位数  | R/W | 比特名         | 功能说明                     |

|-------|-----|-----|-------------|--------------------------|

|       |     |     |             | 0: Disable<br>1: Enable  |

| 0x2C  | 7:0 | R/W | rx_rssi_thr | 接收 RSSI 门限值, 参考 Reg28[5] |

| 0x56  | 7:0 | R/W | delta_rssi  | 计算 RSSI 时的预偏移量           |

| 0x64  | 7:0 | R   | rssi        | 读出的值为实际 RSSI 的绝对值        |

### 5.7.1 自动计算 RSSI

自动计算 RSSI 需使能 AGC, 芯片通过内部自动增益计算得到, 在进入接收状态后, 可以读取 Reg64 寄存器的值 rssi\_value[7:0], 步进为 0.5dBm, 且是真实信号 RSSI 的绝对值, 其计算公式如下:

$$\text{RSSI} = -(\text{rssi\_value}/2)$$

其寄存器优化值如下:

- Reg10[3] = 0

- Reg28[4] = 1

- Reg56 = 0xB7

UM2010 在整个接收数据包期间, RSSI 值实时更新到寄存器 Reg64, 当退出接收状态, Reg64 值也恢复到 0; 如果设置寄存器 Reg28[6]=1, 则收到同步字后寄存器 Reg64 值锁定, RSSI 值不再更新, 直到下次重新进入接收时 RSSI 才会被更新。

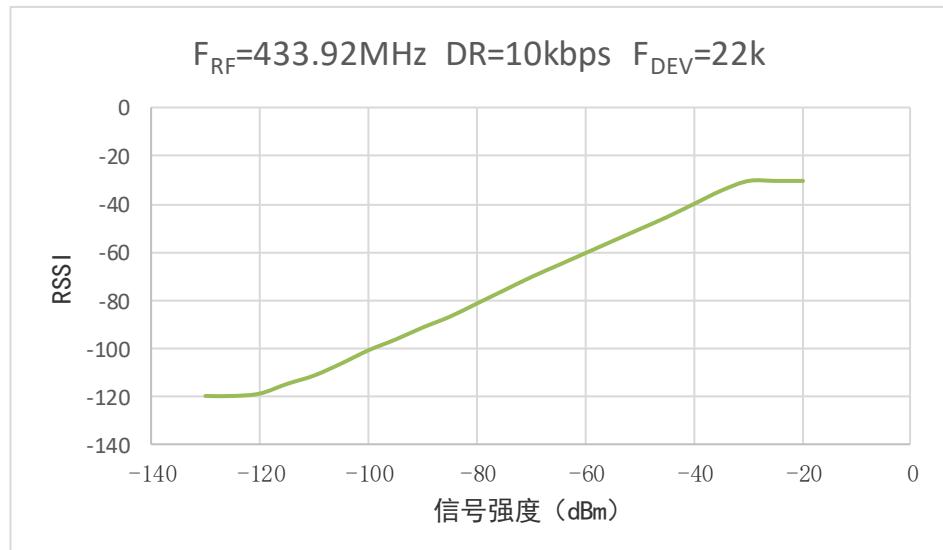

UM2010 在自动计算 RSSI 模式下, 输入功率值与读出的 RSSI 值有很好的对应关系。如果在某些频段或速率在线性区间内读出的值与输入功率值有固定的差值, 可以写寄存器 Reg56 微调偏移量。下图为在  $F_{RF}=433.92\text{MHz}$ ,  $DR=10\text{kbps}$ ,  $F_{DEV}=22\text{K}$  条件下实测的 RSSI 值对应的输入功率。从图上看信号强度在  $[-120\text{dBm}, -35\text{dBm}]$  区间, RSSI 与信号强度存在线性关系。

图 5-2: RSSI 线性图

### 5.7.2 手动调节增益

在正常(G)FSK 模式时，都使用自动增益调节。在 OOK 模式时，可以手动调节增益并计算 RSSI 值。其计算公式为：RSSI= (Reg64/2) – Gain + delta\_rssi

其寄存器优化值设置如下：

- Reg10[3] = 1

- Reg28[6] = 0

- Reg28[4] = 0

- Reg2B[5:0] = 0x3F

进入接收状态后，读取 Reg64 的值，根据 Reg64 的值上下调节 Reg2B 的增益控制。Reg2B 对应增益表如下：

表 5-7: Reg2B 增益控制表

| Reg2B[5:0] | Gain (dBm) |

|------------|------------|

| 111111     | 54         |

| 111110     | 48         |

| 111101     | 42         |

| 111100     | 36         |

| 111000     | 30         |

| Reg2B[5:0] | Gain (dBm) |

|------------|------------|

| 110100     | 24         |

| 110000     | 18         |

| 100000     | 12         |

| 010000     | 6          |

| 000000     | 0          |

### 5.7.3 RSSI 自动过滤功能

RSSI 自动过滤功能，即设置 RSSI 门限值，在解调器接收到前导信号时，会判断 RSSI 值，如接收到的信号强度低于设置的门限，则解调器自动复位，丢弃该信号重新进入接收状态。

如设置信号强度低于-96dBm 时，丢弃该包数据，则进入接收之前设置：

- Reg28[5] = 1

- Reg2C[7:0] = 0xC0

## 5.8 AFC

在接收模式下，自动频率控制 (AFC) 可有效补偿晶体偏差导致的载波频率失配问题。当 AFC 功能启用后，接收信号将被精准校准至中频滤波器的通带范围内，从而在更宽泛的频率偏移区间内实现灵敏度与选择性的最优平衡。值得注意的是，AFC 的正常工作依赖于足够长度的前导码 (preamble) —— 通常需额外增加一定长度（推荐 4 个字节）的前导码序列，以确保 AFC 完成频率校准。

表 5-8: AFC 相关寄存器

| 寄存器地址 | 位数  | R/W | 比特名           | 功能说明                                                 |

|-------|-----|-----|---------------|------------------------------------------------------|

| 0x37  | 7:0 | R/W | csrst_len     | 在补偿功能使能时，找到信号的频谱后连续收到 Reg37*4 个前导后，则认为找到有效的 Preamble |

| 0x38  | 4   | R/W | demod_comp_en | 解调频偏补偿：<br>0: Disable<br>1: Enable                   |

# 6 芯片运行

## 6.1 SPI 接口

芯片内置 SPI 从机模块，通过标准 4 线 SPI 接口与主机 MCU 进行通讯。SPI\_CS、SPI\_CLK、SPI\_MOSI 和 SPI\_MISO。SPI 接口可在最大 16MHz 下工作运行。SPI 接口模式的时钟极性为正，在时钟下降沿采样数据 (CPOL=0, CPHA=1)，在时钟上升沿输出数据，地址和数据部分都是从 MSB 开始传送。芯片内部访问都是以 SPI 读写寄存器的方式，第一个字节为地址，后面跟一个字节的数据。如果在访问 FIFO 对应的地址时，可以在一个 SPI\_CS 为低的周期内按字节方式连续的访问，SPI 接口控制器会自动增加访问地址，在访问 FIFO 数据时，地址和数据之前至少要等 3 个芯片的系统时钟，以便芯片确定 FIFO 指针地址。

在没有晶振时钟时，SPI 接口不能写数据，但仍然可以读寄存器数据。当访问寄存器的时候，SPI\_CS 要拉低。然后首先发送一个 R/W 位，之后是 7 位的寄存器地址。RW=0 表示写，RW=1 表示读。

SPI 默认是 4 线的，在上电后可配置成 3 线。在 SPI 3 线模式下，SPI\_MOSI 同时用于数据输入和输出，在读寄存器数据时，接口会在地址和数据之间对 SPI\_MOSI 的方向进行切换。

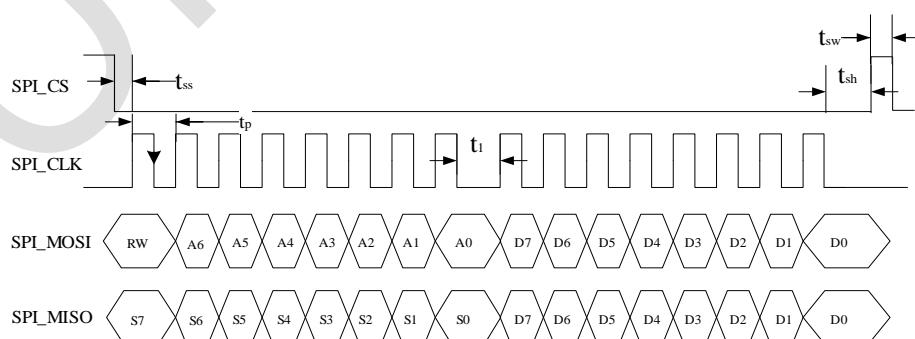

图 6-1: SPI 读写寄存器时序图

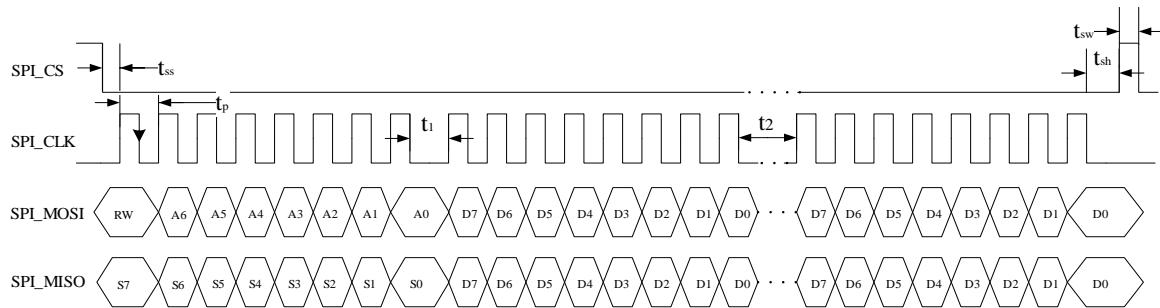

图 6-2: SPI 读写 FIFO 时序图

表 6-1: SPI 时序参数

| 符号               | 最小值   | 说明                     |

|------------------|-------|------------------------|

| $t_{sw}$         | 100ns | 两次 SPI 访问的间隔时间         |

| $t_{ss}, t_{sh}$ | 32ns  | SPI_CS 和 SPI_CLK 的间隔时间 |

| $t_1$            | 32ns  | 地址和数据间隔时间              |

| $t_2$            | 32ns  | 两个寄存器数据读取时间间隔          |

| $t_p$            | 64ns  | SPI_CLK 时钟周期           |

表 6-2: SPI 相关寄存器

| 寄存器地址 | 位数 | R/W        | 比特名 | 功能说明                                                      |

|-------|----|------------|-----|-----------------------------------------------------------|

| 0x57  | 2  | spi_3w_sel | R/W | 三线 SPI 选择:<br>0: 4 线标准 SPI<br>1: 3 线 SPI, 数据线只使用 SPI_MOSI |

## 6.2 FIFO

芯片内置 256 字节 FIFO，分为两组 128 字节的 FIFO 作为发射和接收独立使用。FIFO 独立使用时，发射 FIFO 的数据不会被更新掉，下次如要发同样的数据就不需要再重新写入数据到 FIFO 了。也可以通过寄存器 Reg0E[3]设置成 256 字节共用模式，发射和接收都有 256 字节的 FIFO 可用。

在重新写一帧数据到发射 FIFO 时，应对发射 FIFO 写指针进行清零。在重新读一帧接收 FIFO 数据时，应对接收 FIFO 读指针进行清零。接收写指针和发射读指针芯片内部会自动清零。

表 6-3: FIFO 相关寄存器列表

| 寄存器地址 | 位数  | R/W | 比特名            | 功能说明                                                                |

|-------|-----|-----|----------------|---------------------------------------------------------------------|

| 0x0E  | 3   | R/W | fifo_share_en  | FIFO 共享设置:<br>0: RX 和 TX 各 128 字节 FIFO<br>1: RX 和 TX 共用 256 字节 FIFO |

| 0x50  | 7:0 | R/W | rx_fifo_wr_ptr | RX FIFO 写指针, 写 0x80 清除指针                                            |

| 0x51  | 7:0 | R/W | rx_fifo_rd_ptr | RX FIFO 读指针, 写 0x80 清除指针                                            |

| 0x52  | 7:0 | R/W | rx_fifo_data   | RX FIFO                                                             |

| 0x53  | 7:0 | R/W | tx_fifo_wr_ptr | TX FIFO 写指针, 写 0x80 清除指针                                            |

| 0x54  | 7   | R/W | tx_fifo_rd_ptr | TX FIFO 读指针, 写 0x80 清除指针                                            |

| 0x55  | 7:0 | R/W | tx_fifo_data   | TX FIFO                                                             |

| 0x61  | 3   | R   | fifo_flag      | fifo_flag                                                           |

| 0x9F  | 5:0 | R/W | fifo_empty_thr | TX FIFO 空门限, FIFO 数据低于门限值时<br>fifo_flag 置‘1’                        |

| 0xA0  | 5:0 | R/W | fifo_full_thr  | RX FIFO 满门限, RX FIFO 数据高于门限值<br>时 fifo_flag 置‘1’                    |

### 6.2.1 FIFO 的工作模式

芯片默认提供两个独立的 128-byte 的 FIFO, 分别给 RX 和 TX 使用, 两者互不相干。用户也可以将 fifo\_share\_en 设为 1, 那么两个 FIFO 就可合成一个 256-byte 的 FIFO, 在 TX 和 RX 下共同使用。

### 6.2.2 FIFO 的中断时序

FIFO 的中断包括空中断和满中断, 对于 TX, 设置 fifo\_empty\_thr 为将空阈值, 只要发送的数据低于此门限值, fifo\_flag 产生空中断。对于 RX, 设置 fifo\_full\_thr 为将满阈值, 只要 FIFO 接收的剩余空间低于此门限值, fifo\_flag 产生满中断。

### 6.2.3 FIFO 的应用场景

#### 1. 预先填好数据, 进入 TX 发射

该场景适合发射的数据小于 FIFO 的大小, 其流程如下:

- 初始化寄存器优化值、数据率以及数据包的配置。

- 清 TX FIFO 写指针: Reg53[7:0] = 0x80

- 把数据写入 TX FIFO: Reg55 = data

- 启动发射: Reg60 = 0x40

- 发射完成: 发射完成的判断可查询 Reg61[4], 如果为 1 表示发射完成。也可以通过 nIRQ 这个引脚产生的上升沿中断, 来判断发射完成。

- 如果需要再发射新的数据, 重新清 TX FIFO 写指针, 写入 TX FIFO 数据, 然后启动发射。

## 2. 在 RX 下接收数据

该场景适用于接收数据长度小于 FIFO 大小, 其流程如下:

- 初始化寄存器优化值、数据率以及数据包的配置。

- 写 Reg60 = 0x20 进入接收, 等 MCU 收到 nIRQ 中断。

- 读 Reg61 寄存器, 判断 Reg61[7:4] 是否为 0xD, 如果正确表明收到一包数据。

- 清 RX FIFO 读指针, Reg51 = 0x80。

- 读 RX FIFO 数据 Read Reg(0x52)。

- 读 RSSI (Reg0x64): 根据需要可读出该包的 RSSI 值。

- 写接收命令重新进入接收数据状态。

## 3. 进入 TX 后, 边填数据边发射

该场景适用于每次发送数据超出 FIFO 长度的数据包, 在启动发射后, 需要监控 fifo\_flag 信号, 该信号可以配置到引脚输出, 也可以通过读 Reg61 寄存器获取; 在 TX FIFO 快空时要及时写入数据到 TX FIFO, 保证发射数据流的连续性。其流程如下:

- 初始化寄存器优化值、数据率以及数据包的配置。

- 清 TX FIFO 写指针: Reg53[7:0] = 0x80

- 把数据写入 TX FIFO: Reg55 = data

- 启动发射: Reg60 = 0x40

- 等到 FIFO\_flag 信号或者查询 Reg61[3]是否等于 1, 如产生中断或 Reg61[3]=1, 则继续写往 FIFO 写入数据。

- 直至所有数据发射完成: 发射完成的判断可查询 Reg61[4], 如果为 1 表示发射完成。也可以通过 nIRQ 这个引脚产生的上升沿中断, 来判断发射完成。

- 如果需要再发射新的数据, 重新清 TX FIFO 写指针, 写入 TX FIFO 数据, 然后启动发射。

#### 4. 进入 RX 后, 边读 FIFO 数据边接收

该场景适用于每次接收数据长度超出 FIFO 长度的数据包, 在启动接收后, 需要监控 fifo\_flag 信号, 该信号可以配置到引脚输出, 也可以通过读 Reg61 寄存器获取; 在 RX FIFO 快满时要及时读出数据, 保证接收到的数据不被覆盖。其流程如下:

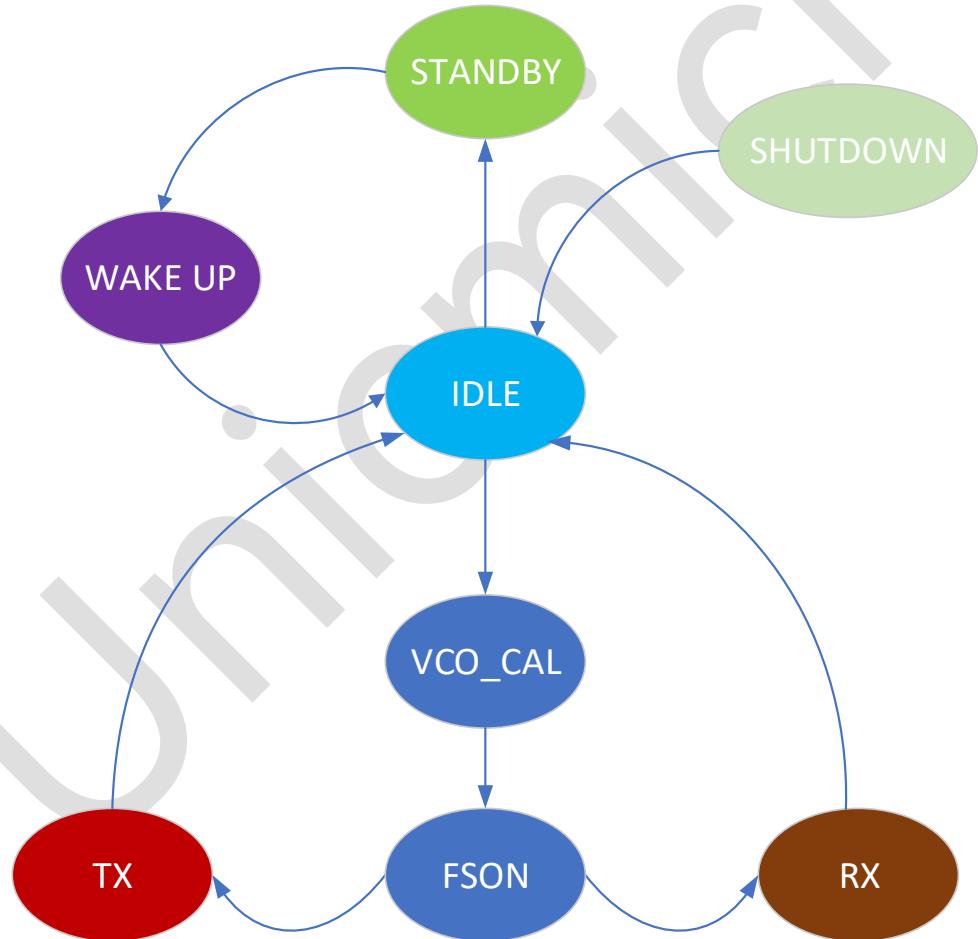

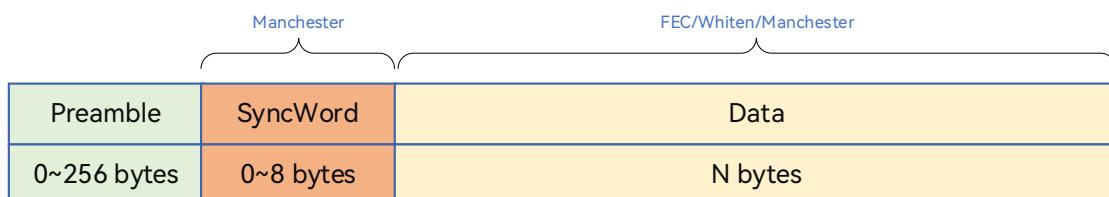

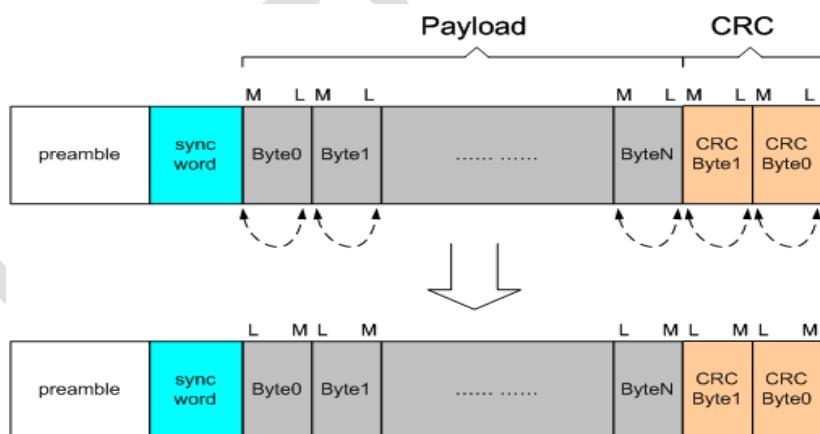

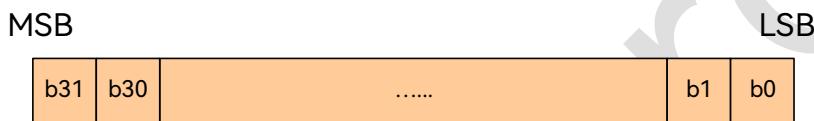

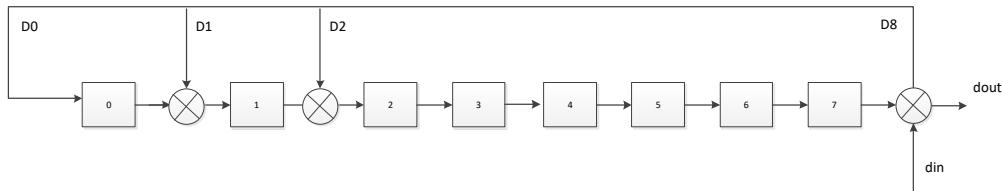

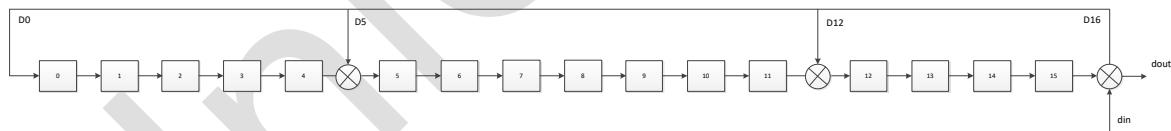

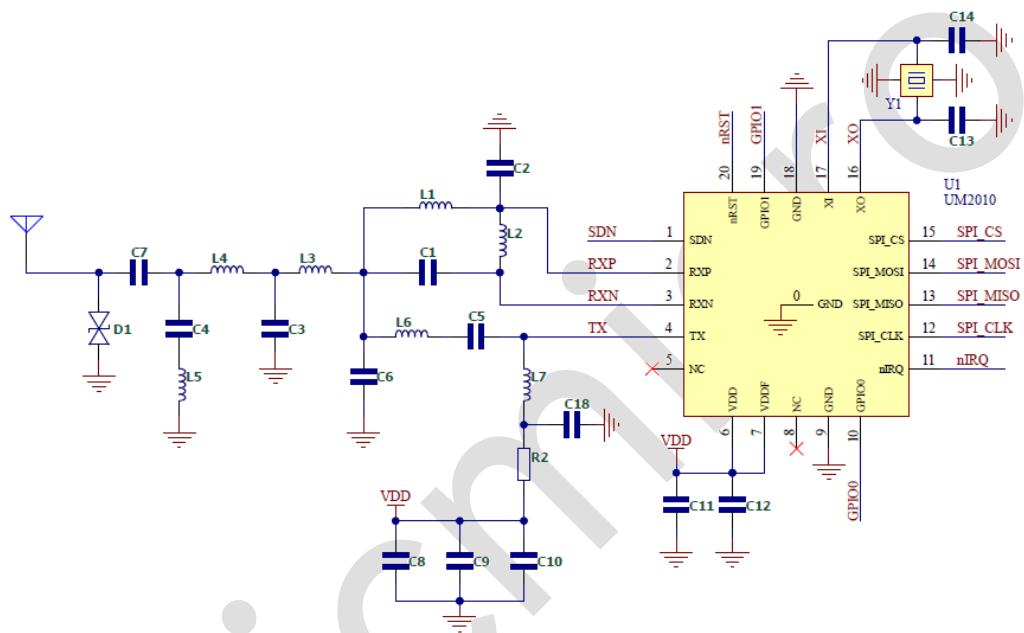

- 初始化寄存器优化值、数据率以及数据包的配置。