# UM2011A

## 单片集成低功耗 Sub-1GHz 射频收发器

### 产品特性

- 功能特点

- 频率范围: 200MHz~1050MHz

- 调制方式: (G)FSK, OOK

- 数据率:

- 0.5 ~ 300 kbps @ (G)FSK

- 0.5 ~ 40 kbps @ OOK

- 支持 NRZ、曼彻斯特、数据白化

- 自动应答/自动重传

- 支持 RSSI 检测

- 可配置包处理机及 64-Byte TX/RX 独立 FIFO

- AGC / AFC

- 支持 FEC

- 支持空中唤醒 (WOR) 和超低功耗接收 (SLP)

- 支持 4 通道自动轮询发射和接收

- 发射功率

- -20dBm ~ +20dBm

- 发射电流 ( $F_{RF}=433MHz$ )

- 10mA @ +0dBm

- 18mA @ +10dBm

- 23mA @ +13dBm

- 80mA @ +20dBm

- 接收灵敏度 ( $F_{RF}=433MHz$ )

- -119dBm @ 1.2kbps

- -112dBm @ 10kbps

- -104dBm @ 100kbps

- -100dBm @ 300kbps

- 接收电流 ( $F_{RF}=433MHz$ )

- 11mA

- 睡眠电流

- 1.7 $\mu$  A

- 关断电流

- 0.1 $\mu$  A

- 接口

- 三线 SPI, 速率最高 6Mbps

- 支持数据直通

- 电气参数

- 工作电压: 1.8V~3.6V

- 工作温度: -40°C~105°C

- 开发支持

- SDK: 软件、文档、工具、参考设计

- EVB 硬件开发板

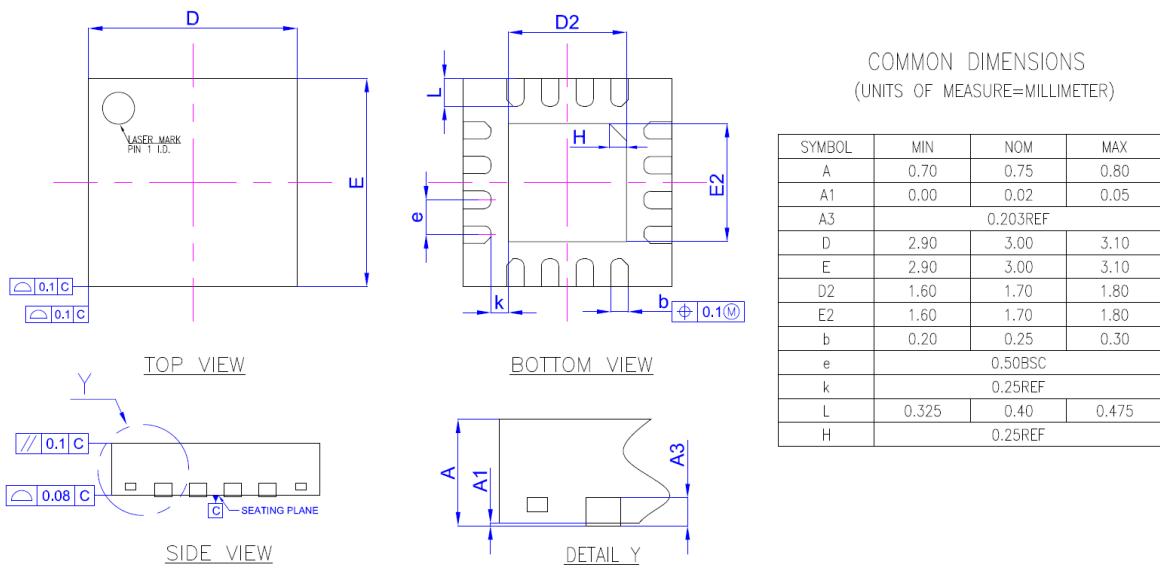

- 选型

| 型号      | 封装    |

|---------|-------|

| UM2011A | QFN16 |

## 目录

|       |                     |    |

|-------|---------------------|----|

| 1     | 产品概述 .....          | 1  |

| 2     | 功能框图 .....          | 2  |

| 3     | 封装及引脚描述 .....       | 3  |

| 3.1   | 封装引脚分布 .....        | 3  |

| 3.2   | 引脚功能描述 .....        | 3  |

| 4     | 电气参数 .....          | 5  |

| 4.1   | 通用工作条件 .....        | 5  |

| 4.2   | 绝对最大额定值 .....       | 5  |

| 4.3   | 功耗 .....            | 6  |

| 4.4   | 接收特性 .....          | 7  |

| 4.5   | 发射特性 .....          | 8  |

| 4.6   | 频率综合器特性 .....       | 8  |

| 4.7   | 状态稳定时间 .....        | 8  |

| 4.8   | 低频振荡器 .....         | 9  |

| 4.9   | 晶体振荡器 .....         | 9  |

| 4.10  | 数字IO输入输出特性 .....    | 10 |

| 5     | 典型参数曲线 .....        | 11 |

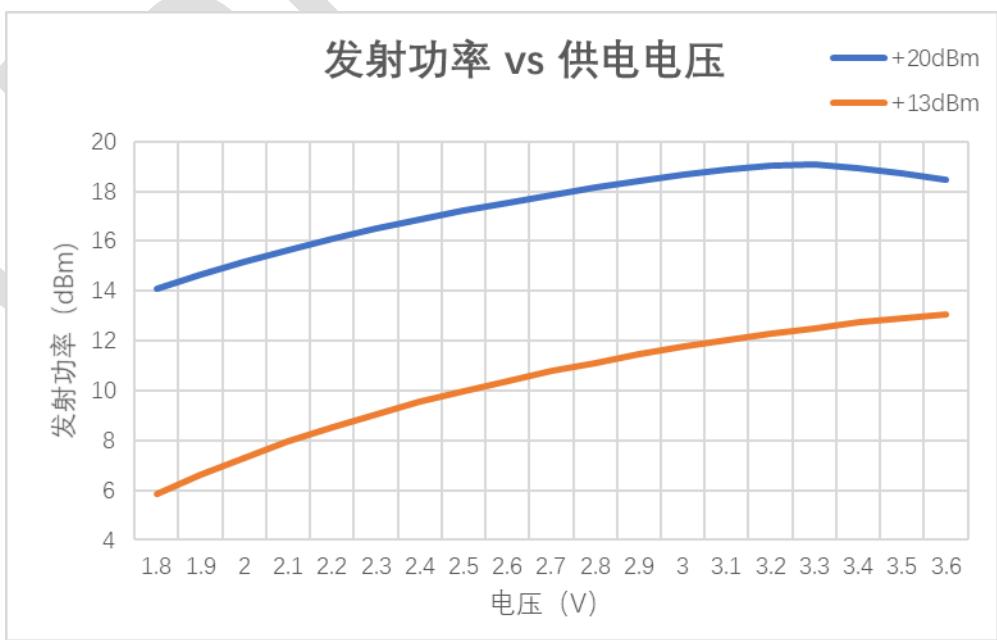

| 5.1   | 发射功率与供电电压曲线图 .....  | 11 |

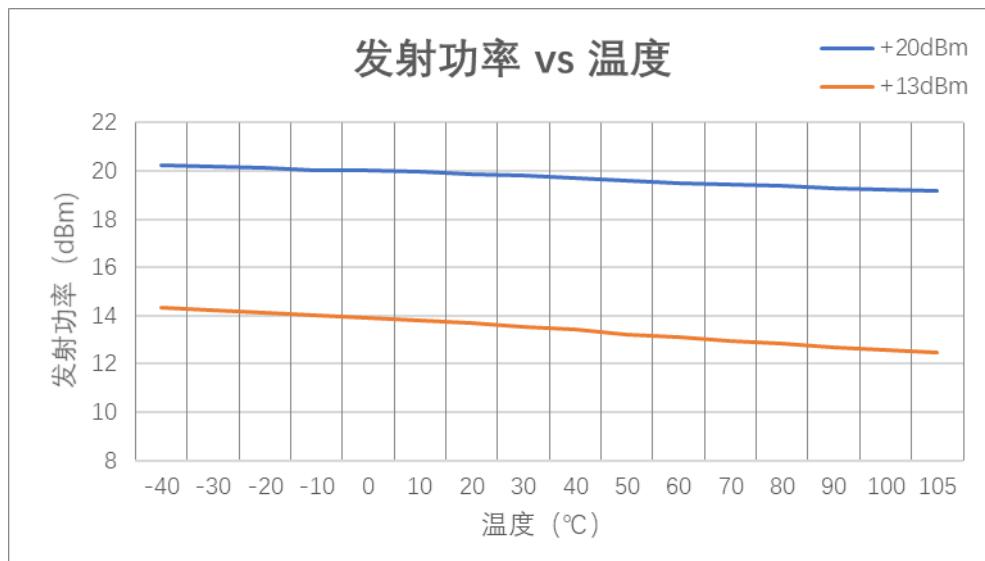

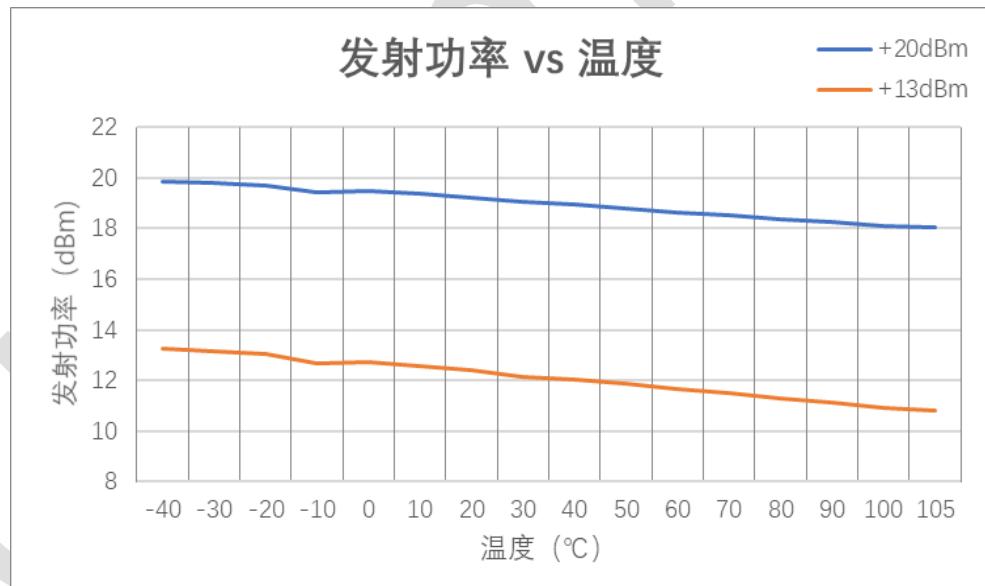

| 5.2   | 发射功率与温度曲线图 .....    | 12 |

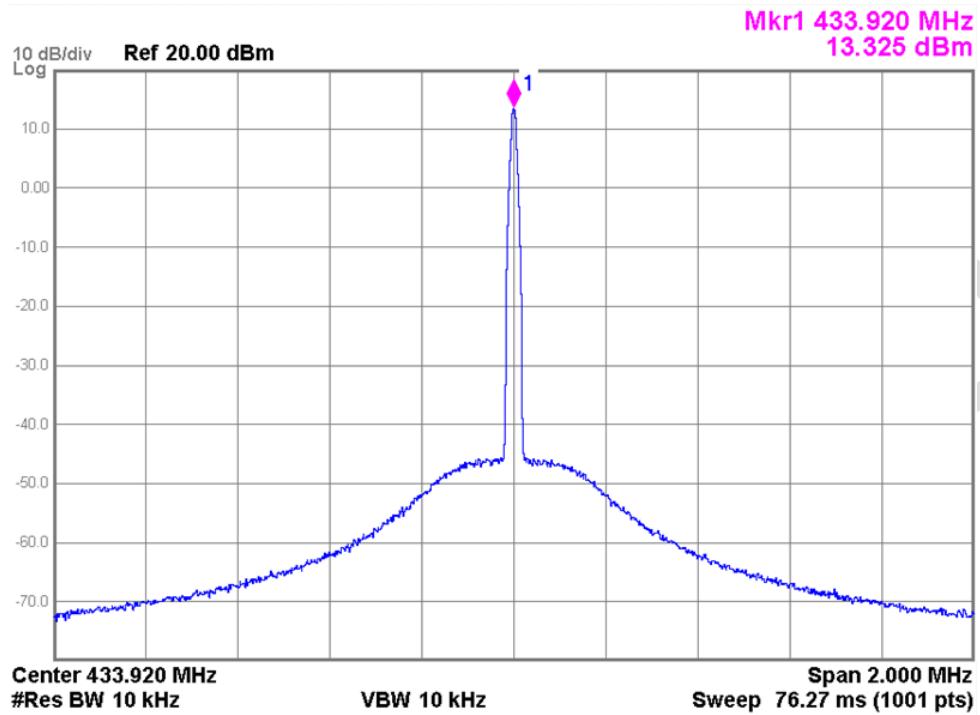

| 5.3   | 发射相位噪声 .....        | 13 |

| 5.4   | 接收灵敏度与供电电压曲线图 ..... | 14 |

| 5.5   | 接收灵敏度与温度曲线图 .....   | 14 |

| 5.6   | 接收电流与供电电压曲线图 .....  | 15 |

| 5.7   | 接收电流与数据率曲线图 .....   | 15 |

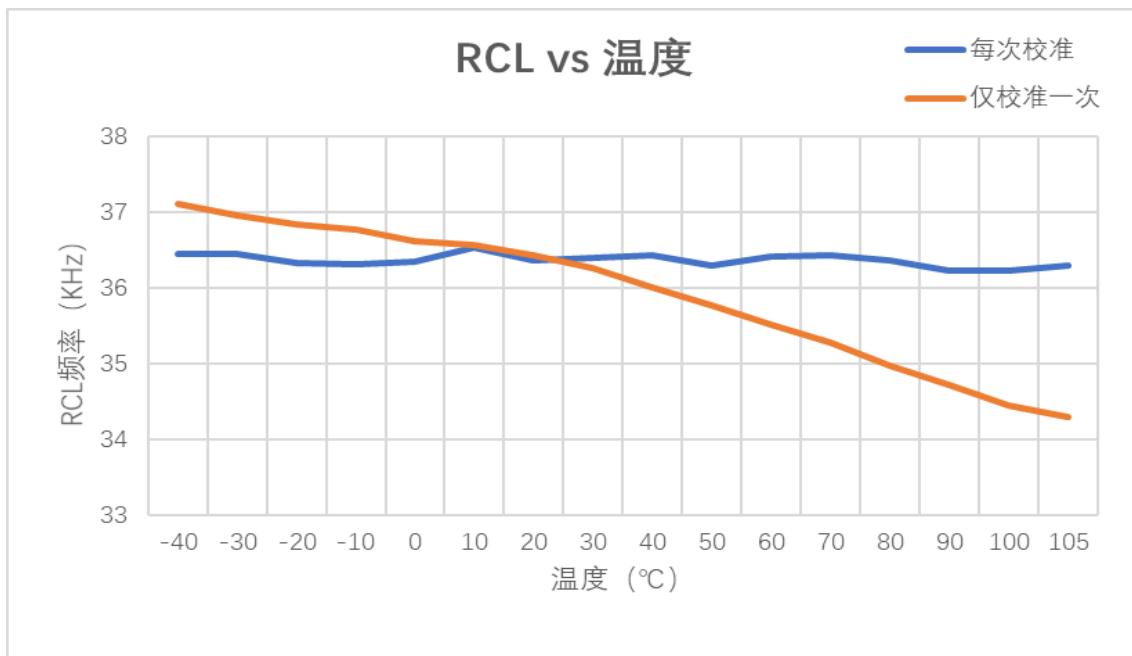

| 5.8   | RCL与温度曲线图 .....     | 16 |

| 6     | 功能描述 .....          | 17 |

| 6.1   | 接收机 .....           | 17 |

| 6.2   | 发射机 .....           | 17 |

| 6.3   | 系统复位 .....          | 18 |

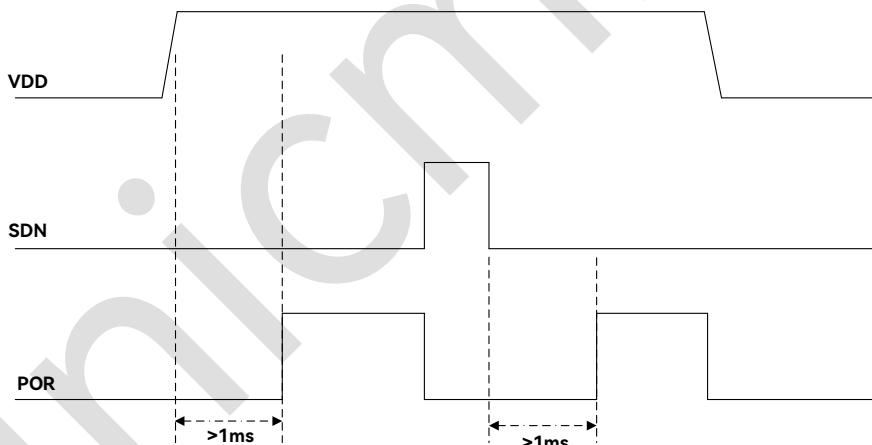

| 6.3.1 | POR复位 .....         | 18 |

| 6.3.2 | 软件复位 .....          | 18 |

| 6.4   | 频率综合器及快速跳频 .....    | 19 |

| 6.5   | 晶体振荡器 .....         | 20 |

| 6.6   | 睡眠定时器（RCL） .....    | 21 |

| 6.7   | 低电压检测（LBD） .....    | 22 |

|       |                       |    |

|-------|-----------------------|----|

| 6.8   | 接收信号强度指示 (RSSI) ..... | 23 |

| 6.9   | 相位跳变检测 (PJD).....     | 24 |

| 6.10  | 自动频率控制 (AFC) .....    | 25 |

| 6.11  | 数据时钟恢复 (CDR) .....    | 25 |

| 7     | 芯片运行 .....            | 27 |

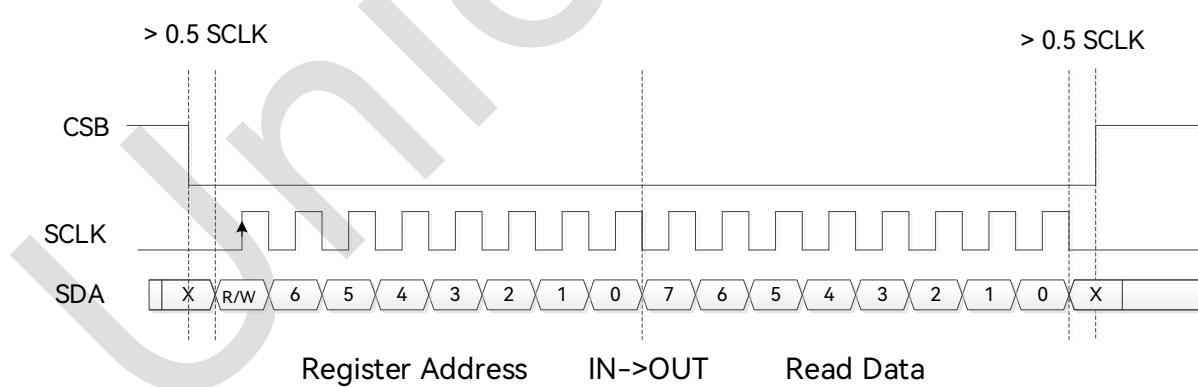

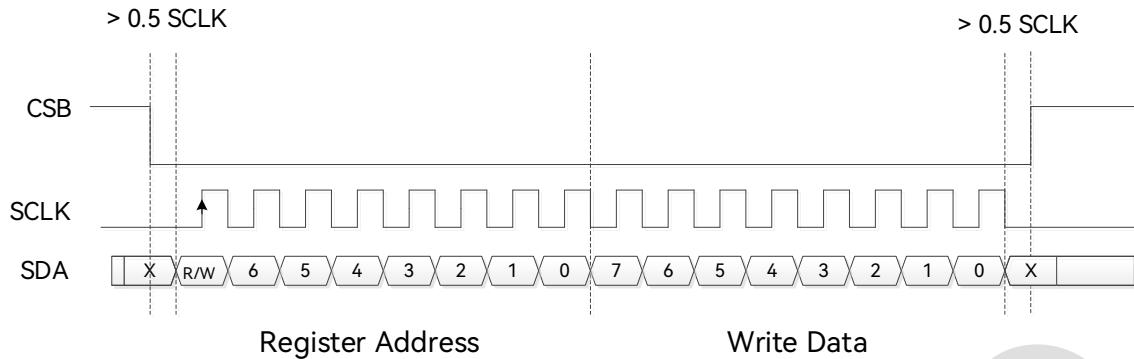

| 7.1   | SPI接口.....            | 27 |

| 7.2   | FIFO .....            | 28 |

| 7.3   | 启动时序与状态机.....         | 30 |

| 7.4   | GPIO和中断 .....         | 32 |

| 8     | 数据包及包处理机制 .....       | 36 |

| 8.1   | 直通模式 .....            | 36 |

| 8.2   | 数据包模式 .....           | 38 |

| 8.2.1 | 数据包模式介绍.....          | 38 |

| 8.2.2 | 数据包操作流程.....          | 40 |

| 8.2.3 | 数据包字段 .....           | 41 |

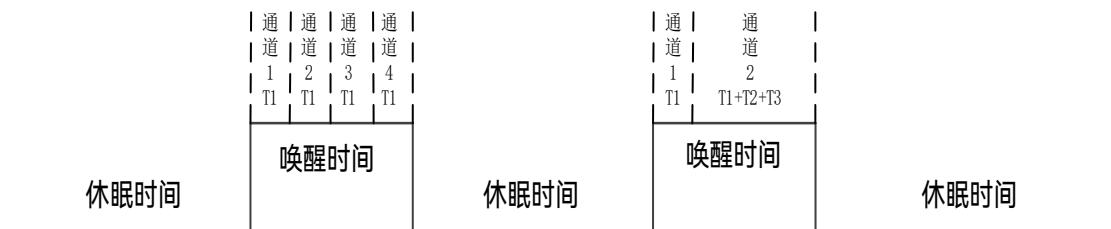

| 9     | 低功耗收发功能 (SLP) .....   | 49 |

| 9.1   | 超低功耗发射模式.....         | 52 |

| 9.2   | 超低功耗接收模式.....         | 52 |

| 9.3   | 多通道发射模式 .....         | 55 |

| 9.4   | 多通道接收模式 .....         | 56 |

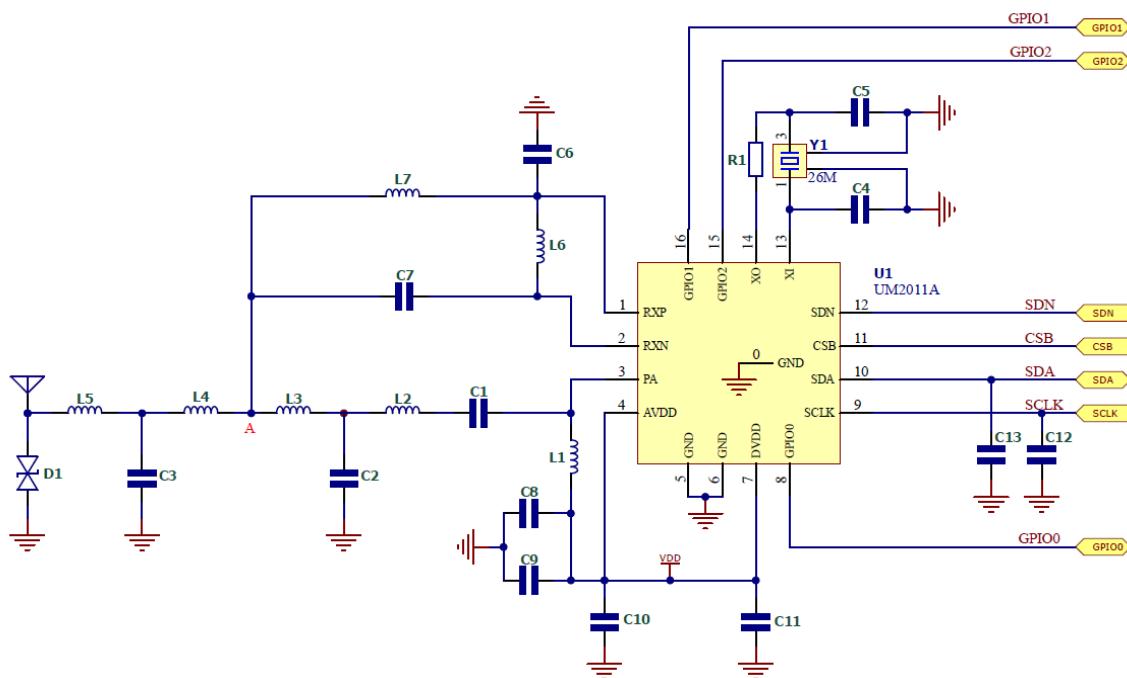

| 10    | 典型应用 .....            | 58 |

| 10.1  | 参考原理图.....            | 58 |

| 10.2  | +13dBm匹配参数.....       | 59 |

| 10.3  | +20dBm匹配参数.....       | 60 |

| 11    | 封装尺寸图 .....           | 61 |

| 12    | 采购信息.....             | 62 |

| 13    | 版本维护 .....            | 63 |

| 14    | 联系我们.....             | 64 |

# 1 产品概述

UM2011A 是一款工作于 200MHz~1050MHz 范围内的低功耗、高性能、单片集成的(G)FSK/OOK 无线收发机芯片。内部集成完整的射频接收机、射频发射机、频率综合器、调制解调器，只需配备简单、低成本的外围器件就可以获得良好的收发性能。支持多种数据包格式及编解码方式，可以灵活满足各种应用需求。

UM2011A 支持独立的 64-byte TX/RX FIFO、丰富的 GPIO 及中断配置、信道侦听、高精度 RSSI、低电压检测、全局关断、手动快速跳频、静噪输出等功能；支持空中唤醒（WOR）和超低功耗接收（SLP），满足低功耗应用。

## 应用场景：

- 工业传感及工业控制

- 安防系统

- 自动抄表

- 无线标签，无线门禁

- 遥控装置，无线玩具

- 智能交通，智慧城市，智能家居

- 智能门锁，资产追踪、无线监控等智能传感器终端应用

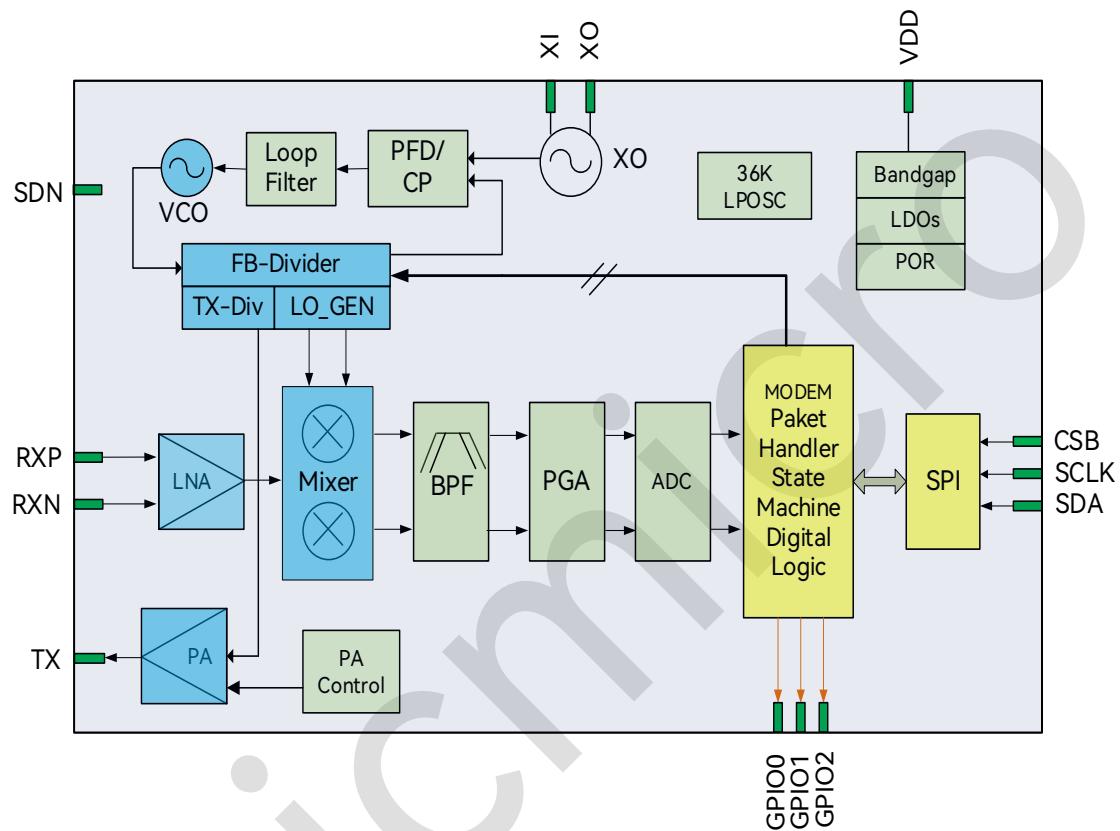

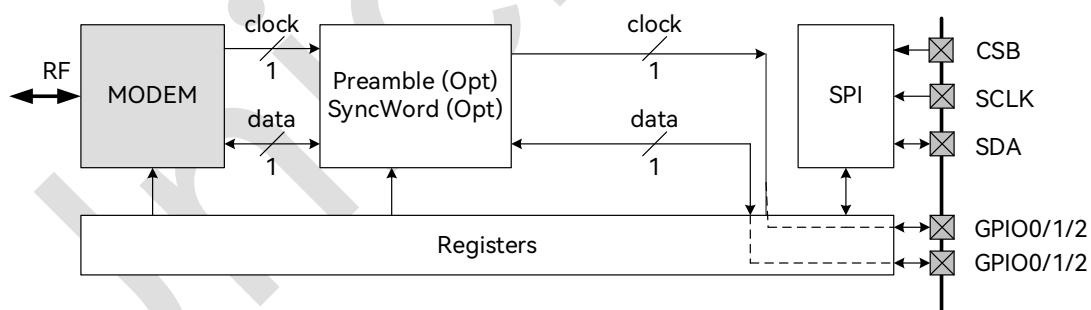

## 2 功能框图

图 2-1: 功能框图

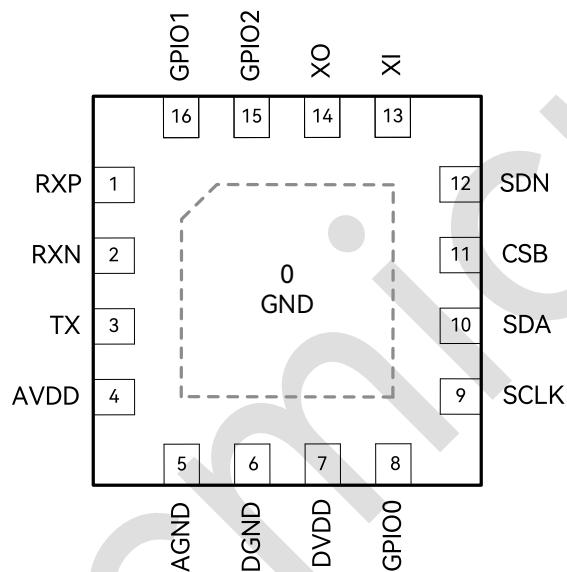

# 3 封装及引脚描述

## 3.1 封装引脚分布

图 3-1: QFN16 封装引脚分布图

## 3.2 引脚功能描述

表 3-1: 引脚功能说明

| 引脚编号 | 管脚名称 | IO 类型 | 关断状态 | 功能描述             |

|------|------|-------|------|------------------|

| 0    | VSS  | G     | -    | 芯片地 (LF PAD) 公共地 |

| 1    | RXP  | RFI   | -    | 射频正端输入           |

| 2    | RXN  | RFI   | -    | 射频负端输入           |

| 3    | TX   | RFO   | -    | 射频 PA 输出         |

| 4    | AVDD | P     | -    | 1.8V~3.6V 模拟电源输入 |

| 5    | AGND | G     | -    | 芯片地              |

| 6    | DGND | G     | -    | 芯片地              |

| 7    | DVDD | P     | -    | 1.8V~3.6V 数字电源输入 |

| 引脚编号 | 管脚名称  | IO 类型 | 关断状态 | 功能描述                |

|------|-------|-------|------|---------------------|

| 8    | GPIO0 | DIO   | HZ   | 可配置多功能脚 GPIO0       |

| 9    | SCLK  | DI    | HZ   | SPI 时钟              |

| 10   | SDA   | DIO   | HZ   | SPI 数据输入输出          |

| 11   | CSB   | DI    | PU   | 片选信号，内部自带 100kΩ 上拉  |

| 12   | SDN   | DI    | HZ   | 芯片全局关断使能，输入高电平时关断芯片 |

| 13   | XI    | AI    | -    | 晶振输入                |

| 14   | XO    | AO    | -    | 晶振输出                |

| 15   | GPIO2 | DIO   | HZ   | 可配置多功能脚 GPIO2       |

| 16   | GPIO1 | DIO   | HZ   | 可配置多功能脚 GPIO1       |

备注： SDN/GPIO0(GPIO1)/GPIO2/SCLK/SDA 内部都不带上下拉， CSB 内部自带 100kΩ 上拉。

说明： RF——射频信号； A——模拟信号； D——数字信号； I——Input； O——Output； G——Ground； P——Power； PU——pull up 上拉； PD——pull down 下拉； HZ——高阻状态。

## 4 电气参数

除非另行声明，否则测试条件为： $V_{DD}=3.3V$ ,  $T_c=25^\circ C$ ,  $F_{RF}=433MHz$ , GFSK, DR=10kbps。所有结果都是在评估板 EVB 上测试得到。

### 4.1 通用工作条件

表 4-1: 主要电气特性参数

| 符号       | 描述     | 测试条件   | 最小值 | 典型值 | 最大值  | 单位     |

|----------|--------|--------|-----|-----|------|--------|

| $V_{DD}$ | 电源电压   | -      | 1.8 | 3.3 | 3.6  | V      |

| $T_c$    | 工作温度   | -      | -40 | -   | 105  | °C     |

| -        | 电源电压斜率 | -      | -   | 1   | -    | mV/μ s |

| $F_{RF}$ | 工作频率范围 | -      | 200 | -   | 1050 | MHz    |

| DR       | 数据率    | (G)FSK | 0.5 | -   | 300  | kbps   |

|          |        | OOK    | 0.5 | -   | 40   | kbps   |

### 4.2 绝对最大额定值

外部条件如果超过“绝对最大额定值”列表中给出的值，可能会导致器件永久性地损坏。这里只是给出能承受永久性损坏的最大载荷，并不意味着在此条件下器件的功能性操作无误。器件长期工作在最大值条件下会影响器件的可靠性。

表 4-2: 芯片绝对最大额定值

| 符号         | 描述          | 测试条件                 | 最小值  | 典型值 | 最大值  | 单位 |

|------------|-------------|----------------------|------|-----|------|----|

| $V_{DD}$   | 电源电压        | -                    | -0.3 | -   | +3.6 | V  |

| $V_{IN}$   | 接口电压        | -                    | -0.3 | -   | +3.6 | V  |

| $T_{OP}$   | 运行温度        | -                    | -40  | -   | +105 | °C |

| $T_J$      | 结温          | -                    | -40  | -   | +125 | °C |

| $T_{stg}$  | 存储温度        | -                    | -50  | -   | +150 | °C |

| $T_L$      | 焊接温度        | -                    | -    | -   | +255 | °C |

| ESD        | 静电放电        | HBM, CDM             | -2   | -   | +2   | kV |

| $I_{LATH}$ | Latch up 电流 | Norm: Jedec78, 105°C | -200 | -   | +200 | mA |

注：TX/XI/XO 管脚 HBM 过 1.5kV。

**警告!** ESD敏感器件。操作过程中需要做好ESD防护，以免芯片性能下降或者功能丧失。

### 4.3 功耗

表 4-3: 功耗参数

| 符号          | 描述            | 测试条件            | 最小值 | 典型值  | 最大值 | 单位      |

|-------------|---------------|-----------------|-----|------|-----|---------|

| $I_{SDN}$   | 关断模式电流        | 寄存器丢失           | -   | 0.1  | -   | $\mu A$ |

| $I_{SLEEP}$ | 休眠模式电流        | 寄存器保持           | -   | 1.7  | -   | $\mu A$ |

| $I_{IDLE}$  | IDLE 状态电流     | 晶振开启            | -   | 1.3  | -   | mA      |

| $I_{RX}$    | 接收状态工作电流      | $F_{RF}=433MHz$ | -   | 11   | -   | mA      |

|             |               | $F_{RF}=868MHz$ | -   | 12   | -   | mA      |

|             |               | $F_{RF}=915MHz$ | -   | 12.1 | -   | mA      |

| $I_{TX}$    | 发射电流@433MHz   | +20dBm          | -   | 80   | -   | mA      |

|             |               | +13dBm          | -   | 23   | -   | mA      |

|             |               | +10dBm          | -   | 18   | -   | mA      |

|             |               | +0dBm           | -   | 10   | -   | mA      |

|             | 发射电流@868MHz   | +20dBm          | -   | 90   | -   | mA      |

|             |               | +13dBm          | -   | 26   | -   | mA      |

|             |               | +10dBm          | -   | 20   | -   | mA      |

|             |               | +0dBm           | -   | 12   | -   | mA      |

| $I_{FS}$    | PLL tune 状态电流 | $F_{RF}=433MHz$ | -   | 5.7  | -   | mA      |

|             |               | $F_{RF}=868MHz$ | -   | 6.5  | -   | mA      |

|             |               | $F_{RF}=915MHz$ | -   | 6.7  | -   | mA      |

## 4.4 接收特性

表 4-4: 接收特性

| 符号                  | 描述                             | 测试条件                                  | 最小值 | 典型值  | 最大值 | 单位  |

|---------------------|--------------------------------|---------------------------------------|-----|------|-----|-----|

| SEN                 | 接收灵敏度<br>@433MHz<br>(BER<0.1%) | DR=1.2kbps<br>$F_{DEV}=2.5\text{kHz}$ | -   | -119 | -   | dBm |

|                     |                                | DR=10kbps<br>$F_{DEV}=10\text{kHz}$   | -   | -112 | -   | dBm |

|                     |                                | DR=100kbps<br>$F_{DEV}=50\text{kHz}$  | -   | -104 | -   | dBm |

|                     |                                | DR=300kbps<br>$F_{DEV}=150\text{kHz}$ | -   | -100 | -   | dBm |

|                     | 接收灵敏度<br>@868MHz<br>(BER<0.1%) | DR=1.2kbps<br>$F_{DEV}=2.5\text{kHz}$ | -   | -116 | -   | dBm |

|                     |                                | DR=10kbps<br>$F_{DEV}=10\text{kHz}$   | -   | -109 | -   | dBm |

|                     |                                | DR=100kbps<br>$F_{DEV}=50\text{kHz}$  | -   | -101 | -   | dBm |

|                     |                                | DR=300kbps<br>$F_{DEV}=150\text{kHz}$ | -   | -97  | -   | dBm |

|                     | 接收灵敏度<br>@915MHz<br>(BER<0.1%) | DR=1.2kbps<br>$F_{DEV}=2.5\text{kHz}$ | -   | -116 | -   | dBm |

|                     |                                | DR=10kbps<br>$F_{DEV}=10\text{kHz}$   | -   | -109 | -   | dBm |

|                     |                                | DR=100kbps<br>$F_{DEV}=50\text{kHz}$  | -   | -101 | -   | dBm |

|                     |                                | DR=300kbps<br>$F_{DEV}=150\text{kHz}$ | -   | -97  | -   | dBm |

| P <sub>in_max</sub> | 最大输入信号功率                       | -                                     | -   | +10  | -   | dBm |

| Co_REJ              | 同频干扰                           | -                                     | -   | 9    | -   | dB  |

| Im_REJ              | 镜像抑制                           | -                                     | -   | -35  | -   | dB  |

| 1CH_REJ             | 第一邻道抑制                         | 200kHz 信道间隔, 带相<br>同调制的干扰             | -   | -35  | -   | dB  |

| 2CH_REJ             | 第二邻道抑制                         | 400kHz 信道间隔, 带相<br>同调制的干扰             | -   | -45  | -   | dB  |

| 3CH_REJ             | 第三邻道抑制                         | 600kHz 信道间隔, 带相<br>同调制的干扰             | -   | -52  | -   | dB  |

| 符号    | 描述 | 测试条件            | 最小值 | 典型值 | 最大值 | 单位 |

|-------|----|-----------------|-----|-----|-----|----|

| Block | 阻塞 | 10MHz 偏移, 连续波干扰 | -   | -72 | -   | dB |

## 4.5 发射特性

表 4-5: 发射特性

| 符号                | 描述         | 测试条件 | 最小值 | 典型值 | 最大值  | 单位  |

|-------------------|------------|------|-----|-----|------|-----|

| P <sub>out</sub>  | 输出功率       | -    | -20 | -   | +20  | dBm |

| P <sub>step</sub> | 输出功率调节     | -    | -   | 1   | -    | dB  |

| t <sub>ramp</sub> | PA ramp 时间 | -    | 0   | -   | 1024 | μ s |

## 4.6 频率综合器特性

表 4-6: 频率综合器特性

| 符号                  | 描述               | 测试条件                    | 最小值 | 典型值  | 最大值  | 单位     |

|---------------------|------------------|-------------------------|-----|------|------|--------|

| F <sub>XTAL</sub>   | 晶振参考频率           | -                       | -   | 26   | -    | MHz    |

| F                   | 输出频率范围           | -                       | 200 | -    | 1050 | MHz    |

| F <sub>RES</sub>    | 输出频率精度           | F <sub>RF</sub> =433MHz | -   | 12   | -    | Hz     |

| t <sub>stable</sub> | 频率稳定时间           | -                       | -   | 160  | -    | μ s    |

| PN                  | 相位噪声<br>(433MHz) | 100kHz 频率偏移             | -   | -97  | -    | dBc/Hz |

|                     |                  | 500kHz 频率偏移             | -   | -115 | -    | dBc/Hz |

|                     |                  | 1MHz 频率偏移               | -   | -125 | -    | dBc/Hz |

|                     |                  | 10MHz 频率偏移              | -   | -139 | -    | dBc/Hz |

## 4.7 状态稳定时间

表 4-7: 状态稳定时间

| 符号                    | 参数描述             | 测试条件         | 最小值 | 典型值 | 最大值 | 单位  |

|-----------------------|------------------|--------------|-----|-----|-----|-----|

| t <sub>SDN-SLP</sub>  | Shutdown 到 Sleep | -            | -   | 500 | -   | μ s |

| t <sub>SLP-IDLE</sub> | Sleep 到 IDLE     | -            | -   | 350 | -   | μ s |

| t <sub>SLP-RX</sub>   | Sleep 到 RX       | With VCO Cal | -   | 550 | -   | μ s |

| t <sub>SLP-TX</sub>   | Sleep 到 TX       | With VCO Cal | -   | 550 | -   | μ s |

| t <sub>IDLE-RX</sub>  | IDLE 到 RX        | With VCO Cal | -   | 200 | -   | μ s |

| t <sub>IDLE-TX</sub>  | IDLE 到 TX        | With VCO Cal | -   | 200 | -   | μ s |

| t <sub>FS-RX</sub>    | FS 到 RX          | -            | -   | 40  | -   | μ s |

| t <sub>FS-TX</sub>    | FS 到 TX          | -            | -   | 40  | -   | μ s |

| 符号                                                               | 参数描述    | 测试条件         | 最小值 | 典型值            | 最大值 | 单位      |

|------------------------------------------------------------------|---------|--------------|-----|----------------|-----|---------|

| $t_{RX-TX}$                                                      | RX 到 TX | With VCO Cal | -   | 200            | -   | $\mu s$ |

| $t_{TX-RX}$                                                      | TX 到 RX | With VCO Cal | -   | $t_{RAMP}+200$ | -   | $\mu s$ |

| 注: $t_{SLP-IDLE}$ , $t_{SLP-RX}$ , $t_{SLP-TX}$ 时间和晶体本身的特性有很大关系。 |         |              |     |                |     |         |

## 4.8 低频振荡器

表 4-8: 低频振荡器特性

| 符号                      | 描述                  | 测试条件        | 最小值 | 典型值     | 最大值 | 单位   |

|-------------------------|---------------------|-------------|-----|---------|-----|------|

| $F_{LPOS C}$            | 校准频率                | -           | -   | 36      | -   | kHz  |

| $F_{RES}$               | 校准精度                | 单温校准        | -   | $\pm 2$ | -   | %    |

| -                       | 温度系数 <sup>[1]</sup> | -40 ~ 105°C | -   | 0.06    | -   | %/°C |

| -                       | 电压系数 <sup>[2]</sup> | 1.8 ~ 3.6V  | -   | 0.5     | -   | %/V  |

| $t_{CAL}$               | 校准时间                | -           | -   | 4       | -   | ms   |

| 备注:                     |                     |             |     |         |     |      |

| [1] 校准后, 频率随温度的变化而变化。   |                     |             |     |         |     |      |

| [2] 校准后, 频率随工作电压的变化而变化。 |                     |             |     |         |     |      |

## 4.9 晶体振荡器

表 4-9: 晶体振荡器特性

| 符号                                                               | 描述                    | 测试条件 | 最小值 | 典型值 | 最大值 | 单位       |

|------------------------------------------------------------------|-----------------------|------|-----|-----|-----|----------|

| $F_{XTAL}$                                                       | 晶体振荡频率                | -    | -   | 26  | -   | MHz      |

| $R_{m_xtal}$                                                     | 晶体等效电阻                | -    | -   | -   | 60  | $\Omega$ |

| $C_{LOAD}$                                                       | 晶体负载电容                | -    | -   | 15  | -   | pF       |

| $t_{XTAL}$                                                       | 晶体起振时间 <sup>[1]</sup> | -    | -   | 350 | -   | $\mu s$  |

| $ppm_{XTAL}$                                                     | 晶体频率容差 <sup>[2]</sup> | -    | -   | 20  | -   | ppm      |

| 备注:                                                              |                       |      |     |     |     |          |

| [1] 晶体起振时间和晶体的特性有很大关系。                                           |                       |      |     |     |     |          |

| [2] 晶体频率容差值包括晶体初始误差以及由负载、老化、温度等因素引起的频率误差。总的频率误差需要满足接收滤波器带宽设置的要求。 |                       |      |     |     |     |          |

## 4.10 数字 IO 输入输出特性

表 4-10: 数字 IO 输入输出特性

| 符号         | 描述        | 测试条件     | 最小值          | 典型值 | 最大值          | 单位  |

|------------|-----------|----------|--------------|-----|--------------|-----|

| $V_{IH}$   | 高电平输入     | -        | $0.8*V_{DD}$ | -   | $V_{DD}$     | V   |

| $V_{IL}$   | 低电平输入     | -        | 0            | -   | $0.2*V_{DD}$ | V   |

| $I_{LEAK}$ | 输入漏电流     | -        | -            | -   | 100          | nA  |

| $V_{OH}$   | 高电平输出     | 1mA 负载电流 | $V_{DD}-0.4$ | -   | -            | V   |

| $V_{OL}$   | 低电平输出     | 1mA 负载电流 | -            | -   | $V_{SS}+0.4$ | V   |

| $F_{SCL}$  | CLK 频率    | -        | -            | -   | 6            | MHz |

| $t_{CH}$   | CLK 为高时间  | -        | 80           | -   | -            | ns  |

| $t_{CL}$   | CLK 为低时间  | -        | 80           | -   | -            | ns  |

| $t_{CR}$   | CLK 上升沿时间 | -        | -            | -   | 64           | ns  |

| $t_{CF}$   | CLK 下降沿时间 | -        | -            | -   | 64           | ns  |

## 5 典型参数曲线

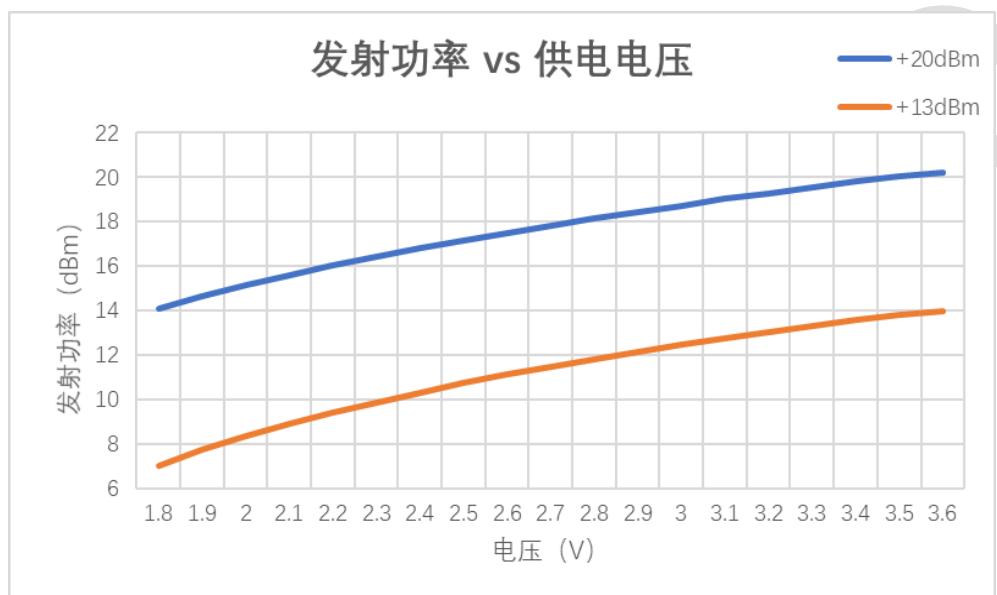

### 5.1 发射功率与供电电压曲线图

测试条件:  $F_{RF} = 433\text{MHz}$ , GFSK,  $P_{out} = +13\text{dBm}/+20\text{dBm}$

测试条件:  $F_{RF} = 868\text{MHz}$ , GFSK,  $P_{out} = +13\text{dBm}/+20\text{dBm}$

## 5.2 发射功率与温度曲线图

测试条件:  $F_{RF} = 433\text{MHz}$ , GFSK,  $P_{out} = +13\text{dbm}/+20\text{dBm}$

测试条件:  $F_{RF} = 868\text{MHz}$ , GFSK,  $P_{out} = +13\text{dbm}/+20\text{dBm}$

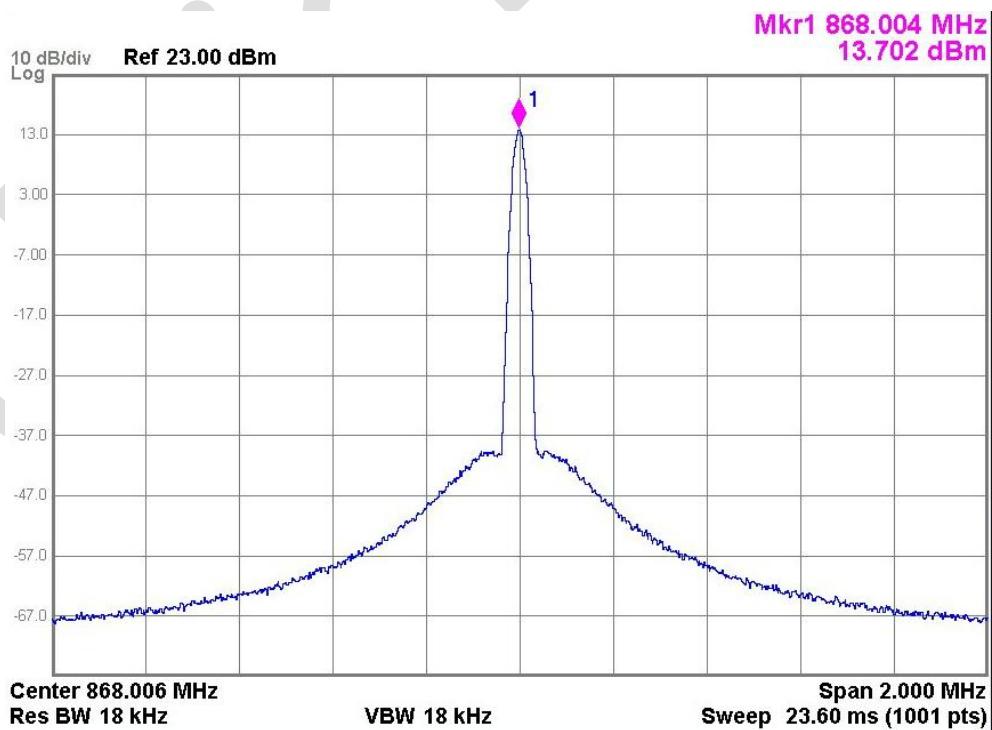

## 5.3 发射相位噪声

测试条件:  $F_{RF} = 433\text{MHz}$ , GFSK,  $P_{out} = +13\text{dBm}$

测试条件:  $F_{RF} = 868\text{MHz}$ , GFSK,  $P_{out} = +13\text{dBm}$

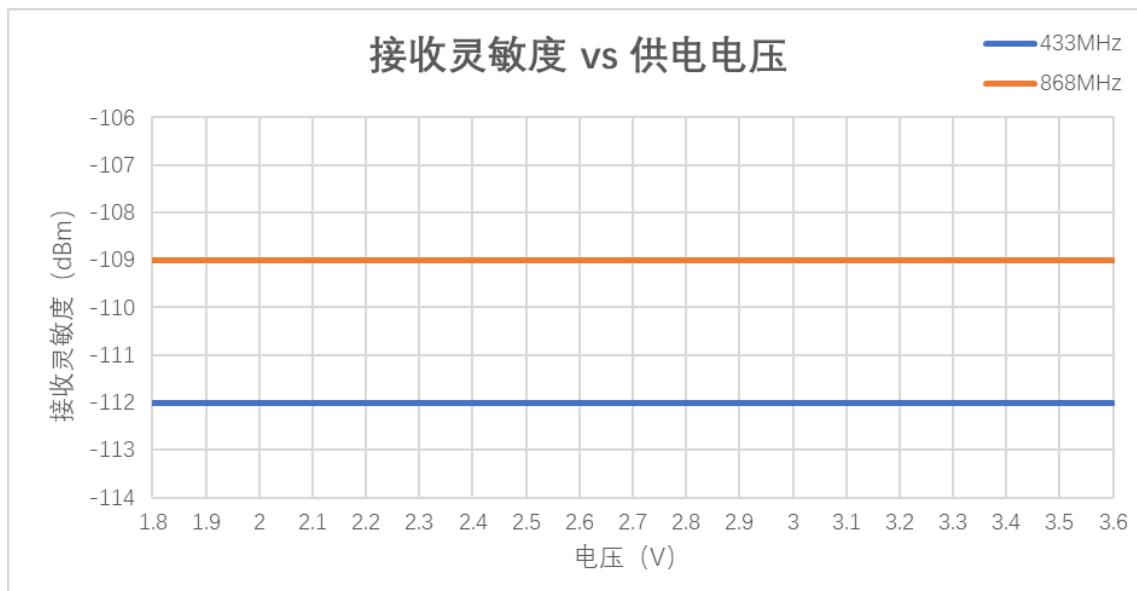

## 5.4 接收灵敏度与供电电压曲线图

测试条件: GFSK, DR = 10kbps,  $F_{dev}$  = 10kHz,  $F_{RF}$  = 433MHz/868MHz

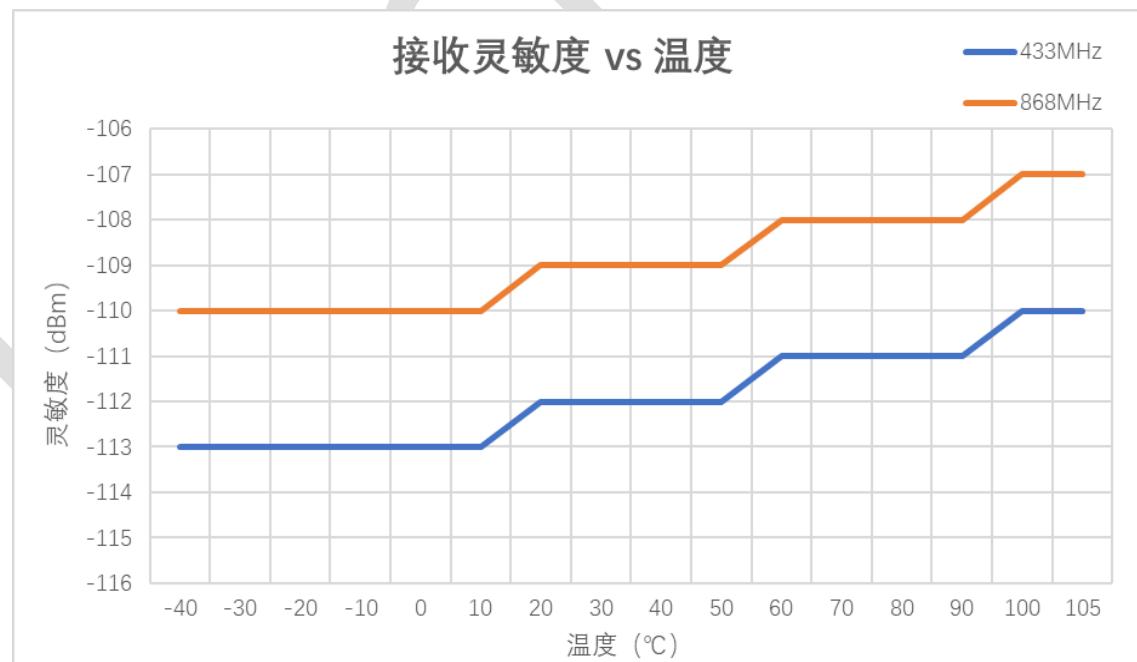

## 5.5 接收灵敏度与温度曲线图

测试条件: GFSK, DR = 10kbps,  $F_{dev}$  = 10kHz, VDD = 3.3V,  $F_{RF}$  = 433MHz/868MHz

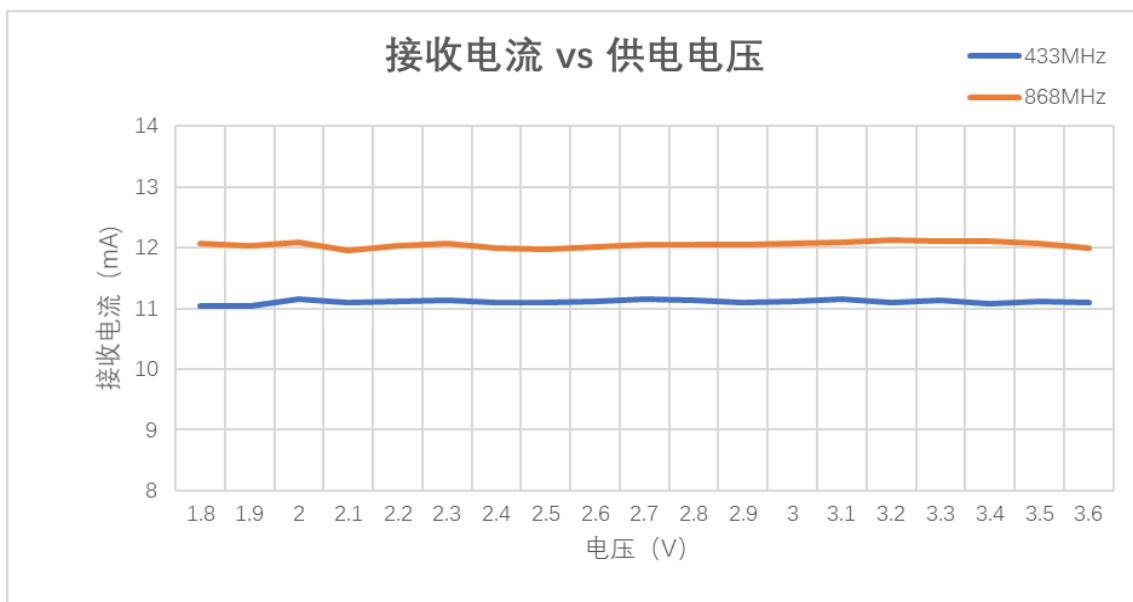

## 5.6 接收电流与供电电压曲线图

测试条件: GFSK, DR = 10kbps,  $F_{dev}$  = 10kHz,  $F_{RF}$  = 433MHz/868MHz

## 5.7 接收电流与数据率曲线图

测试条件: VDD = 3.3V, GFSK,  $F_{RF}$  = 433MHz/868MHz

## 5.8 RCL 与温度曲线图

测试条件: VDD = 3.3V

注: 每次校准: 即到达温度后重新进行 RCL 校准。

仅校准一次: 即在常温 (25°C) 下进行一次 RCL 校准, 达到温度后不进行校准。

# 6 功能描述

UM2011A 是一款高集成度的 sub-1GHz 无线收发机。支持 OOK、2-(G)FSK 调制解调方式，支持 Direct 和 Packet 数据处理模式，支持三线 SPI 接口、多功能 GPIO、超低功耗接收和全局关断功能。

## 6.1 接收机

芯片集成了低功耗、高性能的低中频架构接收机。天线接收到的射频信号经过低噪声放大器放大之后，由正交混频器下变频至中频。I/Q 两路中频信号进一步通过复数带通滤波器（BPF）、可编程放大器（PGA）放大到合适的幅度，然后由 ADC 转换到数字域。芯片在数字域完成镜像抑制、中频滤波、基带滤波和 OOK/(G)FSK 解调等功能。解调后的数据在直通模式下可以通过 GPIO 管脚直接输出，也可以在包模式下通过 SPI 从内部 FIFO 中读取。

## 6.2 发射机

UM2011A 发射机采用基于频率综合器的单点调制电路结构。内部的高效率 class-E 功率放大器可以输出最高 20dBm 的功率，输出功率可以在 -20dBm 至 +20dBm 范围内调节，调节精度为 1dB。在 GFSK 模式下，发射数据经过高斯滤波之后再送入频率综合器进行调制，使得发射频谱更为集中。为了降低 PA 开关过程中引起的频谱杂散和毛刺，并削弱对 VCO 的牵引，PA 的输出功率引入了缓慢升降机制（PA Ramp）。当 PA Ramp 打开时，PA 输出功率可以在设置好的速率下缓慢上升至所需的幅度，以降低不需要的频谱成份。

发射机支持包模式和直通模式。包模式下，数据先填入内部的 FIFO，芯片会自动按照配置完成相应的包处理然后由发射机发射出去。直通模式下，发射数据可以通过 GPIO 直接输入并发射出去。

## 6.3 系统复位

芯片内部集成了上电复位 (POR) 和软件复位。上电复位在芯片上电时产生复位信号来复位整个系统；软件复位是通过 SPI 写命令的方式对芯片进行软复位操作，软复位有两种方式，一种复位整个数字系统（SPI 接口、寄存器、FIFO 和数字内核都进行复位），另一种只复位数字内核（SPI 接口、寄存器和 FIFO 不进行复位）。

### 6.3.1 POR 复位

重新上电或者退出全局关断模式 (SDN 拉低) 后，芯片会触发上电复位 (POR)，复位之后芯片默认处于休眠 (Sleep) 状态。上电稳定或 SDN 拉低后，至少等待 0.5ms 的时间（建议 1ms 以上）再进行 SPI 操作。

图 6-1：POR 复位时序图

### 6.3.2 软件复位

软件复位是通过 SPI 写命令的方式对芯片进行软复位操作，芯片除了在 Power Off 状态外的所有状态，都可以通过 SPI 写指令进行软复位操作。

1. 复位整个数字系统（SPI 接口、寄存器、FIFO 和数字内核都进行复位）

复位整个系统是 SPI 写入复位指令复位整个芯片，芯片复位后回到 Sleep 状态，所有寄存器丢失，需要重新初始化系统，复位系统流程如下：

- a) SPI 写指令：Reg7D=0x02，使能复位

- b) SPI 写指令：Reg7C=0x8F，写复位命令进行复位

2. 复位数字内核（SPI 接口、寄存器和 FIFO 不进行复位）

复位数字内核是写入复位可掉电的数字部分，如芯片工作在 Power off 和 Sleep 状态外的其他状态时，写入数字内核复位指令，复位完成后芯片工作在 IDLE 状态，寄存器和 FIFO 的数据都不丢失，复位内核流程如下：

- a) SPI 写指令：Reg7D=0x02，使能复位

- b) SPI 写指令：Reg7D=0x06，使能数字复位

- c) SPI 写指令：Reg7D=0x00，数字部分正常工作

表 6-1：软件复位相关寄存器

| 寄存器地址 | 位数  | R/W | 比特名            | 功能说明                                                                |

|-------|-----|-----|----------------|---------------------------------------------------------------------|

| 0x7C  | 7:0 | R/W | command        | 0x8F: RST，复位命令，复位芯片所有数字部分，pw_srst_en 需为 1。                          |

| 0x7D  | 2   | R/W | pw_digcore_RST | 除 SPI 接口、寄存器组、FIFO、RC36K 定时器以外的 digcore 数字模块复位：<br>0: 正常工作<br>1: 复位 |

|       | 1   | R/W | pw_srst_en     | srst 复位命令和 pw_digcore_RST 复位控制使能                                    |

## 6.4 频率综合器及快速跳频

该芯片内部集成了高精度的 Sigma Delta 小数分频频率综合器，在 200MHz~1050MHz 范围内产生精准的载波频率。载波频率可以通过两种方式进行设置：

1. 寄存器直接设置，信道频率由 ch\_freq 寄存器决定。

2. 查表方式，信道频率由 ch\_freq + ch\_step \* ch\_index 计算决定。

通过查表方式，可以通过改写 ch\_index 一个寄存器的值来完成频点切换，实现快速跳频功能。

信道切换时间主要由 VCO 校准和稳定时间决定，约为 160μ s。

注：单次校准之后，如果芯片的工作温度发生大幅度变化，VCO 需要重新校准（重新进入 RX 或 TX 即可）。

表 6-2：频率综合器及快速跳频相关寄存器

| 寄存器地址 | 位数  | R/W | 比特名            | 功能说明                                                                                                                                                                         |

|-------|-----|-----|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x00  | 7:0 | R/W | ch_freq[7:0]   | 信道频率分频比设置 ch_freq[7:0],<br>ch_freq[29:0]={reg03[5:0],reg02,reg01,reg00},<br>低 22bit 为小数，高 8 位为整数。<br>Ch_freq=rf_freq/ref_freq * (2^22), rf_freq 为信道<br>频率值, ref_freq 为晶振频率值。 |

| 0x01  | 7:0 | R/W | ch_freq[15:8]  | 信道频率分频比设置 ch_freq[15:8]                                                                                                                                                      |

| 0x02  | 7:0 | R/W | ch_freq[23:16] | 信道频率分频比设置 ch_freq[23:16]                                                                                                                                                     |

| 0x03  | 7:6 | R/W | lo_div[1:0]    | 频段选择：<br>00: 800MHz~1050MHz<br>01: 400MHz~525MHz<br>10: 267MHz~350MHz<br>11: 200MHz~262MHz                                                                                   |

|       | 5:0 | R/W | ch_freq[29:24] | 信道频率分频比设置 ch_freq[29:24]                                                                                                                                                     |

| 0x04  | 7:0 | R/W | ch_step[7:0]   | 信道 ch_step[7:0]。<br>Ch_step[9:0]=step_freq/ref_freq * (2^16),<br>step_freq 为信道 step 频率值, 单位为 MHz。                                                                            |

| 0x05  | 7   | R/W | ch_index_en    | 信道频率计算方式选择：<br>0: 信道频率由 ch_freq 设置<br>1: 信道频率由 ch_freq+step*ch_index 计算                                                                                                      |

|       | 1:0 | R/W | ch_step[9:8]   | 信道 ch_step[9:8]                                                                                                                                                              |

| 0x06  | 7:0 | R/W | ch_index[7:0]  | 信道序号                                                                                                                                                                         |

## 6.5 晶体振荡器

晶体振荡器用于为锁相环提供基准时钟，为数字模块提供系统时钟。负载电容取决于晶体指定 C<sub>L</sub> 参数。XI 与 XO 之间的总的负载电容应该等于 CL，以使晶体准确振荡在参考值范围内。

$$C_L = \frac{1}{\frac{1}{C_1} + \frac{1}{C_2}} + C_{PCB} + C_{IC}$$

C<sub>1</sub> 和 C<sub>2</sub> 分别为晶体两端挂的负载匹配电容，C<sub>PCB</sub> 为 PCB 寄生引入的等效电容（约 0.5pF）。C<sub>IC</sub> 为芯片 XI 和 XO 管脚引入的等效电容（约 2.5pF）。晶体的等效串联电阻应在指定规格之内，以

保证晶体能可靠起振。也可以用一个外部信号源连接至 XI 管脚来取代传统的晶体。外部时钟信号的峰峰值在 300mV 到 700mV 之间，并通过隔直电容耦合到 XI 管脚。晶体的精度越高，接收性能越好。UM2011A 推荐使用负载电容 (CL) 为 15pF，精度为 10ppm 的 26MHz 晶体，板级外挂的负载匹配电容 C1 和 C2 的容值约 24pF。

## 6.6 睡眠定时器 (RCL)

UM2011A 集成了一个由 RCL 低功耗振荡器 (LPOSC) 驱动的睡眠定时器，RCL 默认校准到 36kHz，配合相应的信号检测机制可以实现 Duty Cycle 工作模式和空中唤醒 (WOR) 功能。睡眠时间可以从 0.0278 ms 至 59,651,413 ms 范围内配置。

校准后，校准温度点 RCL 振荡器的频率精度控制在±2%左右。但校准后的频率会随着温度和电压的改变而漂移，因此，实际工作中如果温度或电源电压发生大幅变动，建议重新进行频率校准。

RC36K 校准流程如下：

1. 写指令：RegC1=0xB4，校准 RCL 为 36kHz。

2. 写指令：Reg7C=0x80，使芯片进入 IDLE 状态。

3. 写指令：RegC0=0xC0，使能 RCL 模块和校准命令。

4. 写指令：Reg7C=0x84，启动 RCL 校准。

5. 等待校准完成，默认配置大概在 4ms 左右，也可以通过读取 Reg66[7]校准完成标志来判断。

表 6-3：睡眠定时器相关寄存器

| 寄存器地址 | 位数  | R/W | 比特名          | 功能说明                                                   |

|-------|-----|-----|--------------|--------------------------------------------------------|

| 0x66  | 7   | R   | rcl_cal_done | RCL 校准完成标志                                             |

|       | 6:0 | R   | rcl_ftrim    | RCL 校准值                                                |

| 0x7C  | 7:0 | R/W | command      | 0x80: IDLE 命令<br>0x84: RCL_CAL, RCL 校准命令，只有在 IDLE 状态可进 |

| 0xC0  | 7   | R/W | rcl_en       | RCL 电路使能：<br>0: Disable<br>1: Enable                   |

| 寄存器地址 | 位数  | R/W | 比特名         | 功能说明                                                                                |

|-------|-----|-----|-------------|-------------------------------------------------------------------------------------|

|       | 6   | R/W | rcl_cal_en  | RCL 校准使能:<br>0: Disable<br>1: Enable                                                |

| 0xC1  | 7:0 | R/W | rcl_std     | Rcl 校准目标值                                                                           |

| 0xC3  | 3:0 | R/W | Wor_clk_sel | WOR 功能计算器时钟分频选择:<br>0000: 1 分频<br>0001: 2 分频<br>0010: 4 分频<br>...<br>1111: 32768 分频 |

## 6.7 低电压检测 (LBD)

低电压检测的功能开启后，可以产生低压报警中断，也可通过命令扫描 LBD 功能获取电源电压值，检测电压值可以通过 LBD\_VALUE 寄存器读取。

使能 LBD 模块并设定好电压报警门限，如果电源电压低于电压门限，则会产生报警状态，报警状态可通过寄存器读取或直接输出到 GPIO。在开启 LBD 功能后，如果要得到电源电压值，MCU 需要写电压扫描指令，等待 50μ s 后可通过寄存器读取电压检测值。LBD 电压检测不是持续检测，写一次电压扫描指令，芯片会启动一次电压检测。

表 6-4: 低电压检测相关寄存器

| 寄存器地址 | 位数  | R/W | 比特名             | 功能说明                                                                            |

|-------|-----|-----|-----------------|---------------------------------------------------------------------------------|

| 0x56  | 7   | R/W | lbd_warn_int_en | LBD 报警中断使能:<br>0: Disable<br>1: Enable                                          |

| 0x58  | 4   | R/W | lbd_en          | LBD 使能:<br>0: Disable<br>1: Enable                                              |

|       | 3:0 | R/W | lbd_volt        | LBD 电压设置:<br>0000: 2.0V<br>0001: 2.1V<br>0010: 2.2V<br>...<br>1011: 3.1V (Max.) |

| 寄存器地址 | 位数  | R/W | 比特名           | 功能说明             |

|-------|-----|-----|---------------|------------------|

| 0x6A  | 7:4 | R   | lbd_data      | 电压检测值            |

|       | 3   | R   | lbd_warn      | 低电压报警状态          |

| 0x74  | 6   | R/W | lbd_volt_scan | 写 1 启动扫描 LBD 电压值 |

## 6.8 接收信号强度指示 (RSSI)

RSSI 提供调谐信道内的接收信号的强度指示，可实现精确的信号功率测量，用于信道评估和载波检测。信号强度通过对输入信号的幅度计算和 dBm 值转换，再经过 RSSI 滤波器得到较为平滑的 RSSI 值。滤波器的系数可以由寄存器设定。滤波之后用户可以通过读取寄存器获得相应的 RSSI 值。用户可以选择实时输出 RSSI 值，或在接收数据包的各个阶段锁存 RSSI 值。

UM2011A 允许用户设置 RSSI 门限值 RSSI\_THR，与检测到的 RSSI 值进行对比，如果检测到信号强度大于门限就输出 1，否则输出 0。对比的结果可以输出到 RX\_RSSI\_VALID 中断，也可以用于辅助内部超低功耗 (SLP) 模式的运作。

另外，在 WOR 模式使用 RX\_RSSI\_VALID 信号时，可以开启 RSSI 门限自适应算法，根据在不同的环境，自动调节 RSSI 门限值，使误唤醒率始终保持在目标水平。

表 6-5: RSSI 相关寄存器

| 寄存器地址 | 位数  | R/W | 比特名                 | 功能说明                                                                                               |

|-------|-----|-----|---------------------|----------------------------------------------------------------------------------------------------|

| 0x62  | 7   | R   | rx_rssi_valid       | RSSI 有效中断                                                                                          |

| 0x64  | 7:0 | R   | rssi                | RSSI 值, 需要转换 RSSI_VALUE=-(reg0x64/2)                                                               |

| 0x74  | 7   | R/W | clr_rssi_lock_value | 写 1 清除锁定的 RSSI 值                                                                                   |

| 0xBD  | 7:0 | R/W | rx_rssi_thr[7:0]    | rx_rssi_valid 信号阈值设置, 如要设置 -90dBm, 则该寄存器设置 90*2=180                                                |

| 0xBE  | 7:6 | R/W | rssi_lock_sel       | RSSI 锁定选择:<br>00: 不锁定, 实时更新<br>01: preamble_match 锁定<br>10: syncword_match 锁定<br>11: 查找 RSSI MAX 值 |

## 6.9 相位跳变检测 (PJD)

PJD 是指 Phase Jump Detector，即相位跳变检测器，类似于 preamble match 检测器，比 preamble 匹配快，preamble match 采用的是经过 CDR (时钟数据恢复) 同步之后的信号进行匹配，而 PJD 模块是对原始解调信号进行检测。

芯片解调 FSK 信号时，PJD 可用于通过观察接收 preamble 信号的跳变特性，来识别是否为有效的 preamble 信号。检测信号连续相位跳变，且符合数据率预期同时满足 deviation 即可认为是有效的跳变信号，检测有效信号名为 pjd\_valid。

设置的 PJD 跳变检测次数越多，检测就越可靠。如果接收到的信号满足 PJD 检测条件，那么 pjd\_valid 就会输出 1，如果是噪声或者干扰信号，就会输出 0。pjd\_valid 的状态可以通过配置独立输出，或者与 rx\_rssi\_valid 信号进行组合之后输出 rssi\_pjd\_valid，pjd\_valid 或 rssi\_pjd\_valid 可以辅助超低功耗（SLP）接收模式的实现。

在直通模式下，通过将 rxdata\_mask\_sel 寄存器配置成相应的值，可以利用 PJD 来实现 FSK 解调的输出静音功能。

表 6-6: PJD 相关寄存器

| 寄存器地址 | 位数  | R/W | 比特名            | 功能说明                                                                                         |

|-------|-----|-----|----------------|----------------------------------------------------------------------------------------------|

| 0x61  | 2   | R   | rssi_pjd_valid | RSSI_PJD 有效中断                                                                                |

| 0x74  | 3   | R/W | clr_pjd_valid  | 写 1 清除 pjd_valid 信号                                                                          |

| 0xAB  | 7:6 | R/W | pjdrssi_sel    | rssi_pjd_valid 信号选择:<br>00: pjd_valid<br>01: rx_rssi_valid<br>10/11: rx_rssi_valid&pjd_valid |

|       | 5   |     |                | 1: 自动计算数据率<br>0: 由 cdr_std 配置数据率                                                             |

|       | 4   | R/W | pjd_auto_mode  | PJD 检测模块使能:<br>0: Disable<br>1: Enable                                                       |

|       | 3:0 | R/W | pjd_len        | pjd_valid 长度                                                                                 |

## 6.10 自动频率控制 (AFC)

在接收模式下，自动频率控制 (AFC) 可有效补偿晶体偏差导致的载波频率失配问题。集成频率补偿方案主要分为两类：调制解调器频率补偿与锁相环频率补偿。当 AFC 功能启用后，接收信号将被精准校准至中频滤波器的通带范围内，从而在更宽泛的频率偏移区间内实现灵敏度与选择性的最优平衡。值得注意的是，AFC 的正常工作依赖于足够长度的前导码 (preamble) —— 通常需额外增加一定长度（推荐 4 个字节）的前导码序列，以确保 AFC 完成频率校准。

TX 和 RX 之间的频率差异通常是由两者所用晶体的频率偏差导致的，UM2011A 可通过上位机软件配置 TX 和 RX 使用晶体的容差值，并根据这个容差值自动计算 AFC 的探测范围，保证接收机使用尽可能窄的带宽。

表 6-7: AFC 相关寄存器

| 寄存器地址 | 位数  | R/W | 比特名                 | 功能说明                                                                                          |

|-------|-----|-----|---------------------|-----------------------------------------------------------------------------------------------|

| 0x94  | 7:6 | R/W | afc_start_sel       | AFC 功能生效选择：<br>00: always on<br>01: rx_rssi_valid<br>10: rssi_pjd_valid<br>11: preamble_match |

|       | 0   |     | afc_en              | AFC 功能使能：<br>0: Disable<br>1: Enable                                                          |

| 0x95  | 7:6 | R/W | afc_freeze_sel[1:0] | AFC 补偿值冻结选择：<br>00: 不冻结<br>01: preamble_match<br>10: syncword_match<br>11: 直接冻结               |

## 6.11 数据时钟恢复 (CDR)

CDR 系统的基本任务是对接收的数据进行判别，找到最佳采样点恢复出数据，同时恢复出与数据率同步的时钟信号，既可以在芯片内部用于解码，也可以输出到 GPIO 给用户用于采样数据。

UM2011A 接收机包含三种 CDR 系统和自动跟踪 (TRACING) 系统，分别支持不同的应用需求：

- AUTO\_CDR 系统：这个系统是针对数据率不确定，或数据率偏差 15%以上的，且信号中有 4 个字节以上 preamble 信号，接收端可以使用 AUTO\_CDR 系统模式恢复数据，不需要配置准确数据率，只需要配置足够的滤波器带宽即可完成数据时钟恢复和解码。

- COUNTING 系统：这个系统是针对数据率比较准的情况设计的，接收端只需要进行计数采样就可以恢复出数据和时钟。

- 标准 CDR 系统：这个系统需要配置数据率，然后根据接收信号边沿自动同步，在 TRACING 系统关闭的情况下，即可进行稳定的数据解码和时钟恢复，且允许的数据率偏差可达 $\pm 3\%$ ，芯片默认为标准 CDR 模式。

- TRACING 系统：这个系统是针对数据率偏差比较大的情况设计的自动追踪功能，可以自动探测出 TX 发射过来的数据率，并同时快速地调整 RX 本地的数据率，尽量减小两者之间的误差。这个系统可以承受的范围可以大至 $\pm 15\%$ 。TRACING 系统独立于前面三种 CDR 系统，在每种 CDR 情况下都可以选择开启或关闭 TRACING 系统。

# 7 芯片运行

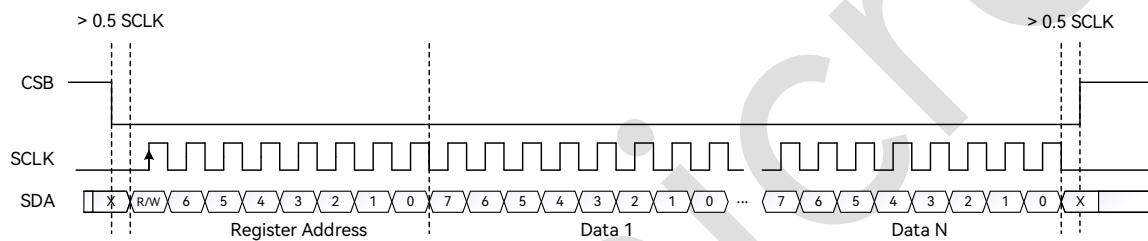

## 7.1 SPI 接口

芯片内置三线 SPI 从机模块，通过三线 SPI 接口 CSB、SCLK、SDA 与主机 MCU 进行通讯。SPI 接口可在最大 6MHz 下工作运行。SPI 接口在时钟下降沿变化数据，在时钟上升沿采样数据(CPOL=0, CPHA=0)。地址和数据都是从 MSB 开始传送。芯片内部访问都是以 SPI 读写寄存器的方式，第一个字节为地址，后面跟一个字节的寄存器数据。地址的 bit7 为读写位，R/W=0 表示读寄存器，R/W=1 表示写寄存器。如果读写连续地址或者访问 FIFO 时，可以在一个 CSB 为低的周期内按字节方式连续的访问，SPI 接口控制器会自动增加访问地址。

注意读寄存器时，芯片将 SDA 脚在最后一位地址的 SCLK 下降沿切换到输出，建议 MCU 在最后一位地址的 SCLK 下降之前，将连接到 SDA 的 IO 口切换到输入，这样可避免 IO 在转换过程中同时为输出，产生电气冲突，引起系统工作异常。

图 7-1: SPI 读寄存器时序

图 7-2: SPI 写寄存器时序

图 7-3: SPI 连续读写寄存器或 FIFO 时序

表 7-1: SPI 相关寄存器

| 寄存器地址 | 位数  | R/W | 比特名          | 功能说明                                     |

|-------|-----|-----|--------------|------------------------------------------|

| 0x57  | 5:4 | R/W | spi_read_sel | SPI 读寄存器使能：<br>00: Disable<br>11: Enable |

## 7.2 FIFO

UM2011A 默认提供两个独立的 64-byte 的 FIFO，分别给 RX 和 TX 使用。RX FIFO 在 RX 模式中存储接收数据，TX FIFO 用于 TX 模式中存储即将发射的数据。用户也可以将两个 FIFO 合成一个 128-byte 的 FIFO，在 TX 或 RX 下使用。

FIFO 可以通过 SPI 接口访问，并为 RX FIFO 和 TX FIFO 分别提供 FIFO 入口地址，方便 SPI 直接操作。用户可以读写 RX FIFO 和 TX FIFO 的指针获取数据。用户如果想要重复发射上一次填入的 TX FIFO 的数据，只要不写 TX FIFO 清除指令，无需要任何操作就可以重复发射数据。通过写命令可以清空 FIFO 数据，也可以恢复 FIFO 指针到零。

TX 时, TX FIFO 读指针在每次启动发射时自动清零; RX 时, RX FIFO 写指针在启动接收时自动清零。

UM2011A 提供了 FIFO 相关的中断源, 作为芯片高效的运作的辅助手段, 为 TX FIFO 提供了 FIFO\_EMPTY\_INT, 为 RX FIFO 提供了 FIFO\_FULL\_INT。同时需要设置 FIFO\_EMPTY\_THR 寄存器和 FIFO\_FULL\_THR 寄存器。在接收时, 当 RX FIFO 空余的数据字节数低于 FIFO\_FULL\_THR 时产生 FIFO 中断; 在发射时, 当 TX FIFO 中未发射的数据字节数低于 FIFO\_EMPTH\_THR 时产生 FIFO 中断。

表 7-2: FIFO 相关寄存器

| 寄存器地址 | 位数  | R/W | 比特名             | 功能说明                                                                                                              |

|-------|-----|-----|-----------------|-------------------------------------------------------------------------------------------------------------------|

| 0x14  | 7   | R/W | pw_fifo_en      | 使能 FIFO 数据在 Sleep 状态下保存:<br>0: Sleep 状态下, FIFO 数据不保存<br>1: Sleep 状态下, FIFO 数据保存                                   |

|       | 6   | R/W | fifo_share_en   | FIFO 使用方式:<br>0: RX_FIFO 和 TX_FIFO 独立使用, 分别为 64 个字节<br>1: RX_FIFO 和 TX_FIFO 联接使用, 在 RX 状态或 TX 状态作为 128 字节 FIFO 使用 |

|       | 5:0 | R/W | fifo_empt_thres | TX 时, TX_FIFO 剩余的数据低于 fifo_empt_thres 时产生 fifo_flag 中断                                                            |

| 0x15  | 5:0 | R/W | fifo_full_thres | RX 时, RX_FIFO 数据空间低于 fifo_full_thres 时产生 fifo_flag 中断                                                             |

| 0x56  | 5   | R/W | fifo_int_en     | FIFO 中断使能:<br>0: Disable<br>1: Enable                                                                             |

| 0x61  | 3   | R   | fifo_flag       | FIFO 空或满中断                                                                                                        |

| 0x75  | 7:0 | R/W | tx_fifo_rd_ptr  | 读该寄存器时为 TXFIFO 读指针, 写 bit7 为 1 时清除 TXFIFO 读指针到 0。                                                                 |

| 0x76  | 7:0 | R/W | tx_fifo_wr_ptr  | 读该寄存器时为 TXFIFO 写指针, 写 bit7 为 1 时清除 TXFIFO 写指针到 0, 写 bit6 为 1 时清除 TXFIFO 数据。                                       |

| 0x77  | 7:0 | R/W | tx_fifo_addr    | TXFIFO 入口地址                                                                                                       |

| 0x78  | 7:0 | R/W | rx_fifo_rd_ptr  | 读该寄存器时为 RXFIFO 读指针, 写 bit7 为 1 时清除 RXFIFO 读指针到 0。                                                                 |

| 0x79  | 7:0 | R/W | rx_fifo_wr_ptr  | 读该寄存器时为 RXFIFO 写指针, 写 bit7 为 1 时清除 RXFIFO 写指针到 0, 写 bit6 为 1 时清除 RXFIFO 数据。                                       |

| 寄存器地址 | 位数  | R/W | 比特名          | 功能说明        |

|-------|-----|-----|--------------|-------------|

| 0x7A  | 7:0 | R/W | rx_fifo_addr | RXFIFO 入口地址 |

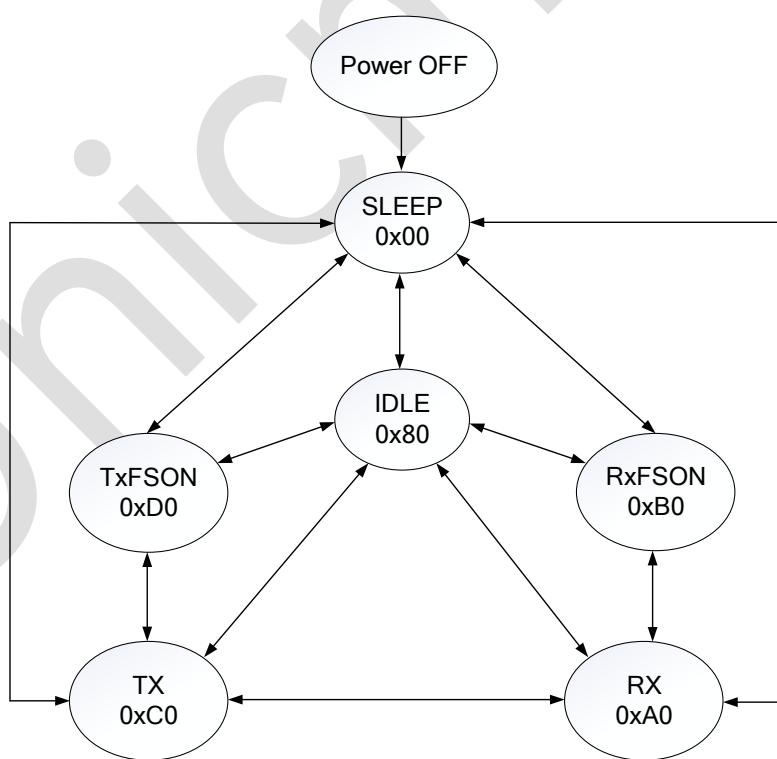

### 7.3 启动时序与状态机

芯片在上电稳定或退出全局关断模式（SDN 拉低）后，至少需要 0.5ms 的时间，POR 才会释放。POR 释放之后，芯片默认停留在 SLEEP 状态，这时芯片可响应 SPI 指令，如果没有 SPI 指令会保持在 SLEEP 状态。如果 SPI 写入 IDLE 指令，芯片开始启动相关电源和晶体，启动稳定时间为 0.35ms（和晶体的特性相关），稳定之后芯片停留在 IDLE 状态，这时可以写 SPI 指令进入任何状态或校正操作。SLEEP 状态下，如果 SPI 写入 TXON、RXON、RXFSION、TXFSION 指令，除了等待晶体稳定的 0.35ms 时间之外，还需要增加 200μ s 左右的 VCO 校准时间和 RX/TX 稳定时间。

芯片一共有 7 种工作状态：POWER\_OFF、IDLE、SLEEP、RXFSION、TXFSION、RX 和 TX，状态转换图如下：

图 7-4：状态转换图

## 1. Power OFF 状态

下电或上电状态下 SDN 拉高，芯片处于关断状态。

## 2. SLEEP 状态

芯片上电默认停留在 SLEEP 状态。其它状态下，芯片写入 SLEEP 命令(0x00)也可以进入 SLEEP 状态。在此状态下，SPI 开启，寄存器的数据保持且可以访问。FIFO 数据也可以设置为保持（默认不保持），但是不能操作 FIFO。

## 3. IDLE 状态

芯片写入 IDLE 命令 (0x80) 进入 IDLE 状态，在此状态下，晶振电路、数字电源开启，寄存器和 FIFO 都可以被读写。由于晶体已经开启，从 IDLE 切换到发射或者接收所需要的时间都会比较短，而从 SLEEP 切换到 IDLE 需要等待晶体开启和稳定后才能完成。

## 4. RXFSON 状态

芯片写入 RXFSON 命令 (0xB0) 进入 RXFSON 状态，RXFSON 是切换到 RX 前的一个过渡状态，接收链路关闭、频综开启，PLL 锁定在 RX 的频点。RXFSON 不能直接切换到 TX，如果在 RXFSON 状态仍然收到 TX 命令，芯片会自动关闭 RXFSON 回到 IDLE 状态，然后再切换到 TX。从 IDLE 切换到 RXFSON 需要  $160\mu s$  (PLL 校正和稳定时间)，从 SLEEP 切换到 RXFSON 需要加上晶体启动和稳定的时间。

## 5. TXFSON 状态

芯片写入 TXFSON 命令 (0xD0) 进入 TXFSON 状态，TXFSON 是切换到 TX 前的一个过渡状态，发射链路关闭、频综开启，PLL 锁定在 TX 的频点。TXFSON 不能直接切换到 RX。如果在 TXFSON 状态仍然收到 RX 命令，芯片会自动关闭 TXFSON 回到 IDLE 状态，然后再切换到 RX。从 IDLE 切换到 TXFSON 需要  $160\mu s$  (PLL 校正、稳定时间)，从 SLEEP 切换到 TXFSON 需要加上晶体启动和稳定的时间。

## 6. RX 状态

芯片写入 RX 命令 (0xA0) 进入 RX 状态，在 RX 状态下接收机的所有模块都会打开。在 RXFSON

状态收到 RX 命令会很快切换到 RX (40μ s RX 稳定时间)。从 IDLE 切换到 RX 需要 200μ s (PLL 校正、稳定和 RX 稳定的时间)。从 SLEEP 切换到 RX 还需要加上晶体启动和稳定时间。在 TX 状态收到 RX 命令直接切换到 RX，需要等待 200μ s (PLL 重新校正、稳定和 RX 稳定的时间) 才能切换成功。

## 7. TX 状态

芯片写入 TX 命令 (0xC0) 进入 TX 状态，在 TX 状态下发射机的所有模块都会打开。在 TXFSON 状态收到 TX 会很快切换到 TX (40μ s RX 稳定时间)。从 IDLE 切换到 TX 需要 200μ s (PLL 校正、稳定和 TX 稳定的时间)。从 SLEEP 切换到 TX 还需要加上晶体启动和稳定的时间。在 RX 状态收到 TX 命令可直接切换到 TX，需要等待 200μ s (PLL 重新校正、稳定和 TX 稳定的时间) 才能切换成功。

表 7-3: 状态机相关寄存器

| 寄存器地址 | 位数  | R/W | 比特名     | 功能说明                                                                                                                                                                                                                                                |

|-------|-----|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x7C  | 7:0 | R/W | command | 0x00: SLEEP, SLEEP 命令<br>0x80: IDLE, IDLE 命令<br>0xc0: TXON, 发射命令<br>0xa0: RXON, 接收命令<br>0xb0: RXFSON, 接收频综打开命令<br>0xd0: TXFSON, 发射频综打开命令<br>0x81: RCCAL, RCBPF 校准命令，只有在 IDLE 或 SLEEP 状态可进入，完成校准后进入 IDLE 状态<br>0x84: RCL_CAL, RCL 校准命令，只有在 IDLE 状态可进 |

## 7.4 GPIO 和中断

UM2011A 有 3 个 GPIO，这 3 个引脚功能都可以配置成不同的输入或者输出。芯片能产生 2 种中断类型，分别为 PKT 和 FIFO 中断。PKT 中断包括了发射完成中断、接收完成中断、Preamble 匹配中断、SyncWord 匹配中断、RSSI 和 PJD 匹配中断；FIFO 中断包括快满中断和快空中断。GPIO 还可配置为直通数据的输入输出和各种时钟输出。

表 7-4: GPIO 和中断相关寄存器

| 寄存器地址 | 位数  | R/W | 比特名             | 功能说明                                                                                                                                              |

|-------|-----|-----|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x52  | 6:4 | R/W | brclk_sel       | GPIO 口时钟输出选择:<br>000: rx_clk<br>001: xtal_core<br>010: fcal_clk<br>011: clk_fsm<br>100: synth_clk<br>101: clk_tx<br>110: clk_rcl<br>111: adc_wclk |

|       | 2   | R/W | gpio2_dir       | GPIO2 方向控制:<br>0: Output<br>1: Input                                                                                                              |

|       | 1   | R/W | gpio1_dir       | GPIO1 方向控制:<br>0: Output<br>1: Input                                                                                                              |

|       | 0   | R/W | gpio0_dir       | GPIO0 方向控制:<br>0: Output<br>1: Input                                                                                                              |

| 0x53  | 7:4 | R/W | gpio1_o_sel     | GPIO1 输出信号选择, 见 GPIO 映射表                                                                                                                          |

|       | 3:0 | R/W | gpio0_o_sel     | GPIO0 输出信号选择, 见 GPIO 映射表                                                                                                                          |

| 0x54  | 3:0 | R/W | gpio2_o_sel     | GPIO2 输出信号选择, 见 GPIO 映射表                                                                                                                          |

| 0x56  | 7   | R/W | lbd_warn_int_en | LBD 报警中断使能:<br>0: Disable<br>1: Enable                                                                                                            |

|       | 6   | R/W | vco_lock_int_en | VCO 错误中断使能:<br>0: Disable<br>1: Enable                                                                                                            |

|       | 5   | R/W | fifo_int_en     | FIFO 中断使能:<br>0: Disable<br>1: Enable                                                                                                             |

|       | 4   | R/W | tx_pkt_int_en   | 发射包完成中断使能:<br>0: Disable<br>1: Enable                                                                                                             |

|       | 3   | R/W | rx_pkt_int_en   | 接收包完成中断使能:<br>0: Disable<br>1: Enable                                                                                                             |

| 寄存器地址 | 位数  | R/W | 比特名              | 功能说明                                                                                                          |

|-------|-----|-----|------------------|---------------------------------------------------------------------------------------------------------------|

|       | 2   | R/W | sync_int_en      | Syncword 中断使能:<br>0: Disable<br>1: Enable                                                                     |

|       | 1   | R/W | preamble_int_en  | Preamble 中断使能:<br>0: Disable<br>1: Enable                                                                     |

|       | 0   | R/W | rssi_pjd_int_en  | RSSI 有效中断使能, 且 RSSI 有效可选组合输出, 由 rssi_pjd_int_sel 选择:<br>0: Disable<br>1: Enable                               |

| 0x57  | 1:0 | R/W | rssi_pjd_int_sel | 00: rx_rssi_valid<br>01: rssi_pjd_valid<br>10: rssi_pjd_valid&preamble_match<br>11: rssi_pjd_valid&sync_match |

表 7-5: GPIO 输出映射说明

| IO_SEL | 名称            | 功能说明                                                                                                                                                  |

|--------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0000   | nirq          | 中断信号包括 rx_pkt_int、tx_pkt_int、preamble_int、syncword_int、fifo_int、vco_lock_int、rssi_pjd_int、lbd_warn_int, 且每个中断分别有中断使能控制, 通过使能控制可以选择一个中断, 或者多个中断或运算后输出。 |

| 0001   | rx_pkt_flag   | 接收包完成标志                                                                                                                                               |

| 0010   | preamble_flag | Preamble match 标志, 接收 preamble 的数量达到目标后锁定, 需要写寄存器清除, 或重新进入接收后自动清除                                                                                     |

| 0011   | syncword_flag | 同步字匹配标志, 接收 syncword 匹配后锁定, 需要写寄存器清除, 或重新进入接收后自动清除                                                                                                    |

| 0100   | fifo_flag     | RXFIFO 快满标志或 TXFIFO 快空标志                                                                                                                              |

| 0101   | clko_sel      | 调试时钟输出, 由 0x52 寄存器中 brclk_sel 选择                                                                                                                      |

| 0110   | rxdata        | 接收时输出解调 BIT 数据 RX DATA, 发射输出调制 BIT 数据 TX DATA                                                                                                         |

| 0111   | vco_lock_flag | VCO 校准异常标志                                                                                                                                            |

| 1000   | crc_error     | 接收 CRC 错误标志                                                                                                                                           |

| 1001   | rssi_pjd_flag | RSSI 有效标志, 由寄存器 rssi_pjd_int_sel 选择 rx_rssi_valid、rssi_pjd_valid、或 rssi_valid 和 preamble_match 的组合输出                                                  |

| 1010   | lbd_warn      | LBD 报警输出, 由 LBD 电路产生                                                                                                                                  |

| 1011   | tr_sw         | TX 切换标志                                                                                                                                               |

| 1100   | ~tr_sw        | TX 切换标志反向                                                                                                                                             |

| IO_SEL | 名称             | 功能说明                                           |

|--------|----------------|------------------------------------------------|

| 1101   | rx_fifo_wrbyte | 指示 RX FIFO 每写入一个 BYTE 的中断，脉冲信号，宽度为一个 symbol 长度 |

| 1110   | 1              | 高电平                                            |

| 1111   | 0              | 低电平                                            |

# 8 数据包及包处理机制

芯片数据模式分为 2 种模式，分别为数据直通模式和数据包模式：

- 数据直通 (Direct) 模式：在 TX 模式下，发射的数据通过 GPIO 串行输入芯片进行发射，在 RX 模式下，芯片接收到的数据通过 GPIO 输出。

- 数据包 (Packet) 模式：在数据包模式下，所有的数据通过 FIFO 读取，且支持各种数据包模式的控制，数据包模式分为 4 种。

## 8.1 直通模式

数据直通模式下，在 TX 模式下，仅支持对 GPIO 输入的数据进行透传；在 RX 模式下，数据解调器数据直接从 GPIO 输出，CDR 模块 bypass，可选择 preamble 或 syncword 匹配后再输出，但需要同时开启 CDR 模块。

图 8-1：直通模式的数据通路

### 直通操作流程：

#### 1. RX 直通接收

在直通模式中，数据从解调器的输出直接通过 GPIO 输出，输出端口可以设置为 GPIO0/1/2。典型的直通模式的 RX 工作顺序如下：

- 1) 寄存器配置 GPIO0/1/2 输出状态。

- 2) 寄存器配置接收直通模式并配置模式为 Mode0。

- 3) 发送 RXON 命令进入接收状态。

- 4) 接收到数据解调后从 GPIO 输出。

- 5) 发送 Sleep / IDLE 来完成接收，节省功耗。

## 2. TX 直通发射

直通模式下，待发射的数据直接 GPIO 送入芯片，数据率只要在芯片使用规范内都能支持发射，典型的直通模式的 TX 工作顺序如下：

- 1) 设置寄存器使能 GPIO 的直通数据功能。

- 2) 设置发射直通模式并设置模式为 Mode0。

- 3) 配置发送 TXON 命令，同时将发射数据送入直通数据端口，数据会立即发送出去。

- 4) 发送 Sleep / IDLE 来完成发射，节省功耗。

表 8-1：直通模式相关寄存器

| 寄存器地址 | 位数  | R/W | 比特名               | 功能说明                                                                                                                                                                          |

|-------|-----|-----|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x21  | 4:3 | R/W | direct_datain_sel | 直通数据引脚选择, 注意要将相应引脚方向设置为输入：<br>00: 无效<br>01: GPIO0<br>10: GPIO1<br>11: 无效                                                                                                      |

|       | 2   | R/W | direct_mode       | 直通模式使能, 发射数据从 GPIO 口直接输入：<br>0: Disable<br>1: Enable                                                                                                                          |

|       | 1:0 | R/W | packet_mode       | 数据帧控制模式：<br>00: 模式 0, 循环发射 TX FIFO 中的数据, 需要 MCU 写命令退出接收或发射状态<br>01: 模式 1, 由寄存器控制数据包长度<br>10: 模式 2, TX FIFO 中的第一个或前 2 个字节作为包长度<br>11: 模式 3, 含有 length、address、seqnum 等多种数据域的模式 |

| 0x52  | 2   | R/W | gpio2_dir         | GPIO2 方向控制：<br>0: Output<br>1: Input                                                                                                                                          |

| 寄存器地址 | 位数 | R/W | 比特名       | 功能说明                                 |

|-------|----|-----|-----------|--------------------------------------|

|       | 1  | R/W | gpio1_dir | GPIO1 方向控制:<br>0: Output<br>1: Input |

|       | 0  | R/W | gpio0_dir | GPIO0 方向控制:<br>0: Output<br>1: Input |

## 8.2 数据包模式

UM2011A 总共支持 4 种数据包模式：Mode0 ~ Mode3。

### 8.2.1 数据包模式介绍

#### 8.2.1.1 Mode 0

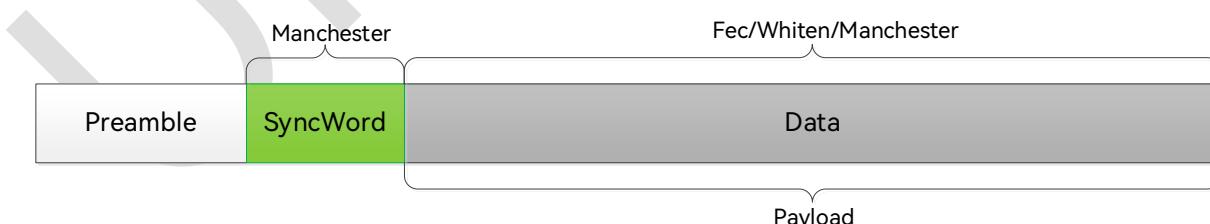

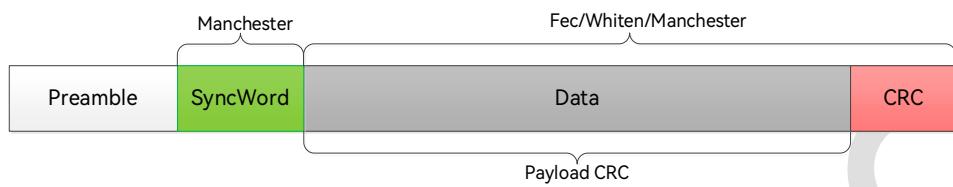

Mode 0 为 FIFO 循环模式，帧格式有 Preamble、SyncWord、Payload 域，Payload 的数据来自 FIFO 中，且不受芯片本身控制。在 TX 模式下，启动 TX 命令后，芯片按照协议格式先发射 Preamble 和 SyncWord 后，芯片会一直循环发射 TX FIFO 中的数据，直到收到其他命令退出 TX 模式。在 RX 模式下，芯片检测到 Preamble 和 SyncWord 后，芯片会将接收到的数据循环写入 RX FIFO 中。

图 8-2: Mode 0 帧格式

### 8.2.1.2 Mode 1

Mode 1 帧格式包括 Preamble、SyncWord、Payload、CRC 域，Payload 域中的 Data 的长度由寄存器控制。

图 8-3: Mode 1 帧格式

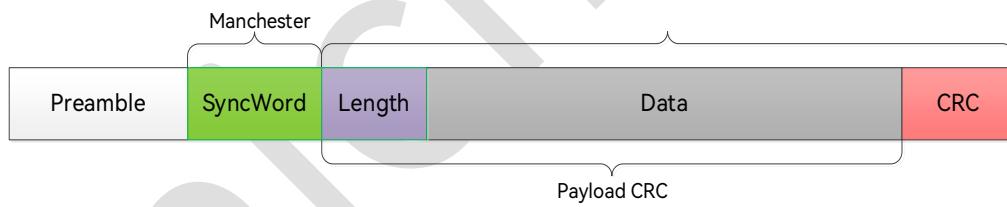

### 8.2.1.3 Mode 2

Mode 2 帧格式包含 Preamble、SyncWord、Payload、CRC 域，其中 Payload 域由 Length 和 Data 组成，Length 在 FIFO 前 1 字节或前 2 个字节，Data 的长度由 Length 控制。

图 8-4: Mode 2 帧格式

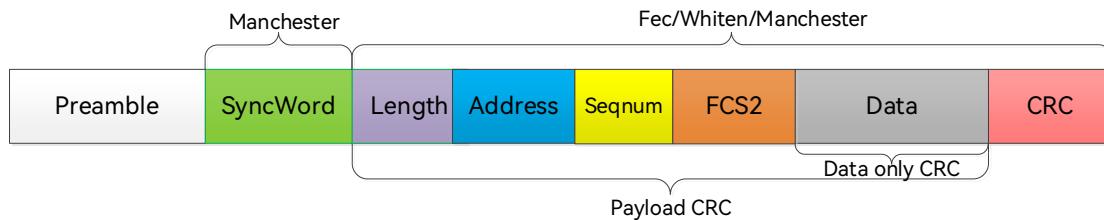

### 8.2.1.4 Mode 3

Mode 3 帧格式包含 Preamble、SyncWord、Payload、CRC 域，其中 Payload 域由 Length、Address、Seqnum、FCS2、Data 组成，Length、Address、Seqnum、FCS2 都由寄存器控制且可以单独控制使能，Data 来自 FIFO，由 Length 控制数据长度。如果 Length 没有使能，发射数据帧格式中不包含 Length，Data 的长度由寄存器直接控制。

图 8-5: Mode 3 帧格式

## 8.2.2 数据包操作流程

### 8.2.2.1 RX 数据包接收

在包模式中，从解调器输出的数据会先被移送至包处理机中进行解码，然后填入 FIFO。包处理机提供多种解码引擎和判断数据有效性的选项，这些可以减轻用户的操作。典型的包模式的 RX 工作顺序如下：

- 1) 初始化寄存器。

- 2) 配置对应的接收模式。

- 3) 发送RXON命令进入接收状态。

- 4) 根据相关的中断状态读取RX FIFO。

- 5) 自动进入IDLE状态以节省功耗。

- 6) 清除接收中断状态。

### 8.2.2.2 TX 数据包发射

在包模式中，可以提前将数据在 IDLE 状态和 FSON 的状态下填入 FIFO 中，或者在芯片发送数据的同时写入 FIFO，或者以上两种方法的结合。典型的包模式的 TX 工作顺序如下：

1. 初始化寄存器。

2. 发送IDLE状态命令，并将数据填入TX FIFO。

3. 寄存器设置发送中断。

4. 配置TXON命令进入发送状态。

5. 在相应的中断状态中将数据写入TX FIFO。

6. 完成N个数据包发送后，会自动退出到IDLE状态，无需发送命令。

### 8.2.3 数据包字段

#### 8.2.3.1 Preamble

Preamble 是发射数据包最前端固定的引导码，主要是用于接收端的信号检测和同步。而 Preamble 的长短直接影响链路建立速度、稳定性和能效，合理的 Preamble 长度可显著提升通信的质量，特别是在复杂环境下。对 TX 来说，Preamble 支持独立使能并可控发射长度。对于接收来说，芯片按 Preamble 匹配长度检测 Preamble Match 成功后会可产生中断通过 GPIO 输出。

表 8-2: Preamble 相关寄存器

| 寄存器地址 | 位数  | R/W | 比特名                   | 功能说明                                                                                          |

|-------|-----|-----|-----------------------|-----------------------------------------------------------------------------------------------|

| 0x2E  | 1   | R/W | tx_preamble_unit      | 发射 preamble 数量单位:<br>0: byte<br>1: bit                                                        |

|       | 0   | R/W | tx_preamble_en        | 发射 preamble 使能:<br>0: Disable<br>1: Enable                                                    |

| 0x2F  | 7:0 | R/W | tx_preamble_len[7:0]  | 发射 preamble 长度低字节，发射长度为 tx_preamble_len+1                                                     |

| 0x30  | 7:0 | R/W | tx_preamble_len[15:8] | 发射 preamble 长度高字节                                                                             |

| 0x31  | 7:0 | R/W | tx_preamble_set       | preamble 设定值，按该值进行发射                                                                          |

| 0x4F  | 7   | R/W | preamble_len_sel      | 在非 WOR 多通道模式时，可以选择加长 preamble_match_len 的配置：<br>0: preamble_match_len[3:0]<br>1: reg0x50[7:0] |

| 0x50  | 7:4 | R/W | ch1_prea_match_len    | WOR 多通道模式时，通道 1 的匹配 preamble 长度设置                                                             |

|       | 3:0 | R/W | preamb_match_len      | 接收 preamble 匹配长度，单位为 bit<br>在 WOR 多通道时<br>preamble_match_len[3:0] 为 ch0 的                     |

| 寄存器地址 | 位数 | R/W | 比特名              | 功能说明                                                                       |

|-------|----|-----|------------------|----------------------------------------------------------------------------|

|       |    |     |                  | preamble_len 配置，在非 WOR 多通道时，由 preamble_len_sel 选择加长 preamble_match_len 的配置 |

| 0x56  | 1  | R/W | preamble_int_en  | Preamble 中断使能：<br>0: Disable<br>1: Enable                                  |

| 0x61  | 6  | R   | preamble_int     | Preamble 中断                                                                |

| 0x74  | 1  | R/W | clr_preamble_int | 写 1 清除 preamble 中断                                                         |

### 8.2.3.2 SyncWord

SyncWord 是数据包通信位于 Preamble 和 Payload 之间的关键标识，直接影响通信的可靠性和安全性，UM2011A 提供灵活的同步字配置选项，可根据应用场景在识别成功率、抗干扰能力和功耗之间取得平衡。UM2011A 支持 SyncWord 的独立使能，并支持自由长度设置，曼切斯特使能，支持 bit 顺序交换、高低位交换，同步字中断。

表 8-3: SyncWord 相关寄存器

| 寄存器地址 | 位数  | R/W | 比特名            | 功能说明                                                                                                                     |

|-------|-----|-----|----------------|--------------------------------------------------------------------------------------------------------------------------|

| 0x32  | 7:4 | R/W | sync_thres     | 同步字检测允许的错误位数                                                                                                             |

|       | 3   | R/W | sync_mancst_en | 同步字曼切斯特编码使能：<br>0: Disable<br>1: Enable                                                                                  |

|       | 2   | R/W | sync_byte_swap | 同步字字节交换使能：<br>0: reg0x33 为 sync_id[7:0], reg0x3a 为 sync_id[63:56]<br>1: reg0x33 为 sync_id[63:56], reg0x3a 为 sync_id[7:0] |

|       | 1   | R/W | sync_bit_order | 同步字 bit 顺序：<br>0: sync_id 的 LSB<br>1: sync_id 的 MSB                                                                      |

|       | 0   | R/W | syncword_en    | 同步字使能：<br>0: Disable<br>1: Enable                                                                                        |

| 0x33  | 7:0 | R/W | sync_id[7:0]   | 同步字配置 sync_id[7:0]，同步字长度由 syncword_len 设置，如 syncword_len 为 0x1f，则使用的同步字为 32bits，具体数据                                     |

| 寄存器地址 | 位数  | R/W | 比特名              | 功能说明                                                                                                                                                                                |

|-------|-----|-----|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |     |     |                  | 由 sync_id[31:0]设置。<br>例如 sync_id[63:0]=0x12345678,<br>syncword_len=0x23 (syncword 长度为<br>36bits), sync_bit_order=1, 则先发射<br>0x45678 的最高位; 如 sync_bit_order=0,<br>则先发射 0x45678 的最低位。 |

| 0x34  | 7:0 | R/W | sync_id[15:8]    | 同步字配置 sync_id[15:8]                                                                                                                                                                 |

| 0x35  | 7:0 | R/W | sync_id[23:16]   | 同步字配置 sync_id[23:16]                                                                                                                                                                |

| 0x36  | 7:0 | R/W | sync_id[31:24]   | 同步字配置 sync_id[31:24]                                                                                                                                                                |

| 0x37  | 7:0 | R/W | sync_id[39:32]   | 同步字配置 sync_id[39:32]                                                                                                                                                                |

| 0x38  | 7:0 | R/W | sync_id[47:40]   | 同步字配置 sync_id[47:40]                                                                                                                                                                |

| 0x39  | 7:0 | R/W | sync_id[55:48]   | 同步字配置 sync_id[55:48]                                                                                                                                                                |

| 0x3A  | 7:0 | R/W | sync_id[63:56]   | 同步字配置 sync_id[63:56]                                                                                                                                                                |

| 0x3B  | 5:0 | R/W | syncword_len     | 同步字 bit 长度, 最长 64bits, 长度为<br>syncword_len+1                                                                                                                                        |

| 0x56  | 2   | R/W | sync_int_en      | Syncword 中断使能:<br>0: Disable<br>1: Enable                                                                                                                                           |

| 0x61  | 7   | R   | syncword_int     | Syncword 中断                                                                                                                                                                         |

| 0x74  | 2   | R/W | clr_syncword_int | 写 1 清除 syncword 中断                                                                                                                                                                  |

### 8.2.3.3 Payload

Payload 是数据包通信中真正承载用户信息的核心部分, UM2011A 支持灵活配置 Payload Data 编码, 支持 NRZ、曼彻斯特、差分曼彻斯特、数据白化、FEC 等编码, 并支持高低位互换。

在不同模式下, Payload Data 长度设置方式不一样, 以下为各个模式设置。

1. Mode 0: Payload Data的长度是由FIFO长度决定, 当FIFO独立使用时, Payload Data的长度为64bytes, 当FIFO共享使用时, Payload Data的长度为128bytes。

2. Mode 1: Payload Data的长度由寄存器payload\_length决定。

3. Mode 2: Payload Data的长度由FIFO第一个字节或者前2个字节决定。

4. Mode 3: 当Length长度使能时, Data域长度由Length域决定。当Length不使能时, Data域长度由寄存器payload\_length决定。

表 8-4: Payload 相关寄存器

| 寄存器地址 | 位数  | R/W | 比特名                  | 功能说明                                                              |

|-------|-----|-----|----------------------|-------------------------------------------------------------------|

| 0x21  | 7   | R/W | payload_bit_order    | Payload bit 顺序:<br>0: LSB 低位在前<br>1: MSB 高位在前                     |

| 0x22  | 7   | R/W | length_2byte_sel     | 选择 1 个或 2 个字节作为包长度控制域:<br>0: 1 字节<br>1: 2 字节                      |

|       | 6   | R/W | length_byte_swap     | 包长度控制域为两个字节时，高低字节顺序交换:<br>0: 低字节在前<br>1: 高字节在前                    |

|       | 5   | R/W | mancst_dif_en        | 差分曼切斯特编码使能:<br>0: Disable<br>1: Enable                            |

|       | 4   | R/W | mancst_inv           | 曼彻斯特编码反向:<br>0: 上升沿为编码 1, 下降沿为编码 0<br>1: 下降沿为编码 1, 上升沿为编码 0       |

|       | 3:2 | R/W | pkt_enc_type         | Payload 数据包编码:<br>00: NRZ 无编码<br>01: 曼彻斯特编码<br>10: 无效<br>11: 交织编码 |

|       | 1:0 | R/W | fec_type             | Payload 数据包 FEC 类型:<br>00: NO FEC<br>01: 1/3 FEC<br>10: 2/3 FEC   |

| 0x3C  | 7:0 | R/W | payload_length[7:0]  | Payload 字节长度                                                      |

| 0x3D  | 7:0 | R/W | payload_length[15:8] | Payload 字节长度                                                      |

#### 8.2.3.4 Length

Length 域仅在 Mode 3 下支持，Length 域支持独立使能，并支持灵活设置。当 Length 使能时，Length 域决定 Mode 3 的 Data 域长度。当 Length 域不使能时，Mode 3 的 Data 域长度由寄存器 payload\_length 决定。

表 8-5: Length 相关寄存器

| 寄存器地址 | 位数  | R/W | 比特名                      | 功能说明                                            |

|-------|-----|-----|--------------------------|-------------------------------------------------|

| 0x22  | 7   | R/W | length_2byte_sel         | 选择 1 或 2 个字节作为包长度控制域:<br>0: 1 字节<br>1: 2 字节     |

|       | 6   | R/W | length_byte_swap         | 包长度控制域为两个字节时, 高低字节顺序交换:<br>0: 低字节在前<br>1: 高字节在前 |

| 0x3C  | 7:0 | R/W | payload_length[7:0]      | Payload 字节长度                                    |

| 0x3D  | 7:0 | R/W | payload_length[15:8]     | Payload 字节长度                                    |

| 0x3E  | 5   | R/W | m3_length_en             | 数据包模式 3 时, 数据长度域控制:<br>0: Disable<br>1: Enable  |

| 0xE8  | 7:0 | R   | m3_rx_length_value[7:0]  | 包模式 3, 接收包长度域低字节                                |

| 0xE9  | 7:0 | R   | m3_rx_length_value[15:8] | 包模式 3, 接收包长度域高字节                                |

### 8.2.3.5 Address

Address 域仅在 Mode 3 下支持, Address 域支持独立使能, 并支持灵活设置、地址过滤等。

表 8-6: Address 相关寄存器

| 寄存器地址 | 位数  | R/W | 比特名                | 功能说明                                                                      |

|-------|-----|-----|--------------------|---------------------------------------------------------------------------|

| 0x3F  | 5:4 | R/W | m3_addr_size       | 数据包模式 3 时, 地址长度为 m3_addr_size + 1                                         |

|       | 3   | R/W | m3_addr_err_mask   | 数据包模式 3 时, 地址错误 mask                                                      |

|       | 2   | R/W | m3_addr_split_mode | 数据包模式 3 时, 将地址分为源地址和目的地址, 在返回 ACK 时, 将收到的源地址和目的地址位置互换:<br>0: 不互换<br>1: 互换 |

|       | 1   | R/W | m3_addr_pos_sel    | 数据包模式 3 时, 地址位置选择:<br>0: address 放在 length 之后<br>1: address 放在 length 之前  |

|       | 0   | R/W | m3_addr_en         | 数据包模式 3 时, 地址域控制:<br>0: Disable<br>1: Enable                              |

| 0x40  | 7:0 | R/W | m3_addr_value[7:0] | 数据包模式 3 时, 地址数据                                                           |

| 寄存器地址 | 位数  | R/W | 比特名                     | 功能说明                                        |

|-------|-----|-----|-------------------------|---------------------------------------------|

| 0x41  | 7:0 | R/W | m3_addr_value[15:8]     | 数据包模式 3 时, 地址数据                             |

| 0x42  | 7:0 | R/W | m3_addr_value[23:16]    | 数据包模式 3 时, 地址数据                             |

| 0x43  | 7:0 | R/W | m3_addr_value[31:24]    | 数据包模式 3 时, 地址数据                             |

| 0x44  | 7:0 | R/W | m3_addr_bitmask[7:0]    | 数据包模式 3 时, 接收地址比较 mask, mask 为‘1’时对应地址位不作比较 |

| 0x45  | 7:0 | R/W | m3_addr_bitmask[15:8]   | 数据包模式 3 时, 接收地址比较 mask, mask 为‘1’时对应地址位不作比较 |

| 0x46  | 7:0 | R/W | m3_addr_bitmask[23:16]  | 数据包模式 3 时, 接收地址比较 mask, mask 为‘1’时对应地址位不作比较 |

| 0x47  | 7:0 | R/W | m3_addr_bitmask[31:24]  | 数据包模式 3 时, 接收地址比较 mask, mask 为‘1’时对应地址位不作比较 |

| 0x6A  | 0   | R   | m3_addr_comp_ok         | 1: 包模式 3, 接收地址匹配正确                          |

| 0xE2  | 7:0 | R   | m3_rx_addr_value[7:0]   | 包模式 3 时, 接收 Address 值                       |

| 0xE3  | 7:0 | R   | m3_rx_addr_value[15:8]  | 包模式 3 时, 接收 Address 值                       |

| 0xE4  | 7:0 | R   | m3_rx_addr_value[23:16] | 包模式 3 时, 接收 Address 值                       |

| 0xE5  | 7:0 | R   | m3_rx_addr_value[31:24] | 包模式 3 时, 接收 Address 值                       |

### 8.2.3.6 Seqnum

Seqnum 域仅在 Mode 3 下支持, 支持独立使能, Seqnum 的数据来源可来自寄存器或者内部计数器。在 TX 模式, Seqnum 作为数据包结构一并发出。在接收中, Seqnum 中自动填入到映射的寄存器, 可以直接读取寄存器值。

表 8-7: Seqnum 相关寄存器

| 寄存器地址 | 位数  | R/W | 比特名                | 功能说明                                                                                            |

|-------|-----|-----|--------------------|-------------------------------------------------------------------------------------------------|

| 0x48  | 2   | R/W | m3_seqnum_bit_size | 数据包模式 3 时, Seqnum 数据长度:<br>0: 8 bits<br>1: 16 bits                                              |

|       | 1   | R/W | m3_seqnum_auto_inc | 数据包模式 3 时, Seqnum 选择:<br>0: Seqnum 数据由{reg49,reg4a}配置<br>1: 由内部 Seqnum 计数器配置,<br>Seqnum 数据自动加 1 |

|       | 0   | R/W | m3_seqnum_en       | 数据包模式 3 时, Seqnum 数据使能:<br>0: Disable<br>1: Enable                                              |

| 0x49  | 7:0 | R/W | m3_seqnum_reg[7:0] | 数据包模式 3 时, Seqnum 域配置值                                                                          |

| 寄存器地址 | 位数  | R/W | 比特名                      | 功能说明                    |

|-------|-----|-----|--------------------------|-------------------------|

| 0x50  | 7:0 | R/W | m3_seqnum_reg[15:8]      | 数据包模式 3 时, Seqnum 域配置值  |

| 0x61  | 1   | R   | m3_seqnum_ok             | 1: 包模式 3, 接收 Seqnum 正确  |

| 0xE0  | 7:0 | R   | m3_rx_seqnum_value[7:0]  | 包模式 3 时, 接收 Seqnum 值    |

| 0xE1  | 7:0 | R   | m3_rx_seqnum_value[15:8] | 包模式 3 时, 接收 Seqnum 值    |

| 0xE6  | 7:0 | R   | m3_seqnum_cnt[7:0]       | 包模式 3 时, 本地 Seqnum 计数器值 |

| 0xE7  | 7:0 | R   | m3_seqnum_cnt[15:8]      | 包模式 3 时, 本地 Seqnum 计数器值 |

### 8.2.3.7 FCS2

FCS2 域仅在 Mode 3 下支持, FCS2 支持独立使能、灵活配置。

表 8-8: FCS2 相关寄存器

| 寄存器地址 | 位数  | R/W | 比特名              | 功能说明                                              |

|-------|-----|-----|------------------|---------------------------------------------------|

| 0x48  | 7   | R/W | m3_fcs2_en       | 数据包模式 3 时, FCS2 数据域使能:<br>0: Disable<br>1: Enable |

|       | 6:4 | R/W | m3_fcs2_bit_size | 数据包模式 3 时, FCS2 域 bit 长度                          |

| 0x4B  | 7:0 | R/W | m3_fcs2_value    | 数据包模式 3 时, FCS2 数据, 最高位表示 ACK request, 其他位保留      |

| 0x6B  | 7:0 | R   | m3_rx_fcs2_value | 包模式 3, 接收 FCS2 域值                                 |

### 8.2.3.8 CRC

CRC 域在 Mode 1/2/3 下支持, CRC 域作为数据校验, 确保数据完整性、可靠性的关键技术, UM2011A 的 CRC 域支持独立使能, 灵活配置, 支持常用的标准多项式。

表 8-9: CRC 相关寄存器

| 寄存器地址 | 位数 | R/W | 比特名              | 功能说明                                                             |

|-------|----|-----|------------------|------------------------------------------------------------------|

| 0x16  | 2  | R/W | crc_err_rxrst    | 收到 CRC 错误时, 状态机选择:<br>0: 正常接收, 置 CRC_ERR 标志<br>1: 丢弃该包数据, 重新进入接收 |

| 0x25  | 7  | R/W | crc_en           | CRC 使能:<br>0: Disable<br>1: Enable                               |

|       | 5  | R/W | crc_rx_infifo_en | 接收的 CRC 值是否需要写入 RX FIFO:<br>0: Disable<br>1: Enable              |

| 寄存器地址 | 位数  | R/W | 比特名                  | 功能说明                                                                        |

|-------|-----|-----|----------------------|-----------------------------------------------------------------------------|

|       | 4   | R/W | crc_bit_order        | CRC bit 顺序:<br>0: LSB<br>1: MSB                                             |

|       | 3   | R/W | crc_inv              | CRC bit 取反:<br>0: Disable<br>1: Enable                                      |

|       | 2   | R/W | crc_byte_swap        | CRC 字节交换使能:<br>0: Disable<br>1: Enable                                      |

|       | 1:0 | R/W | crc_len              | CRC 长度:<br>00: 8 位<br>01: 16 位<br>10: 24 位<br>11: 32 位                      |

| 0x26  | 7:0 | R/W | crc_poly[7:0]        | crc_poly 多项式配置, 见常用多项式                                                      |

| 0x27  | 7:0 | R/W | crc_poly[15:8]       | crc_poly 多项式配置, 见常用多项式                                                      |

| 0x28  | 7:0 | R/W | crc_poly[23:16]      | crc_poly 多项式配置, 见常用多项式                                                      |

| 0x29  | 7:0 | R/W | crc_poly[31:24]      | crc_poly 多项式配置, 见常用多项式                                                      |

| 0x2A  | 7:0 | R/W | crc_init_data[7:0]   | crc_init_data 初始值配置                                                         |

| 0x2B  | 7:0 | R/W | crc_init_data[15:8]  | crc_init_data 初始值配置                                                         |

| 0x2C  | 7:0 | R/W | crc_init_data[23:16] | crc_init_data 初始值配置                                                         |

| 0x2D  | 7:0 | R/W | crc_init_data[31:24] | crc_init_data 初始值配置                                                         |

| 0x3E  | 4   | R/W | m3_crc_sel           | 数据包模式 3 时, CRC 计算数据区域选择:<br>0: 整个 payload 域做 CRC 计算<br>1: 只对 data 域做 CRC 计算 |

| 0x61  | 5   | R   | crc_error            | 1: CRC error                                                                |

表 8-10: 常用多项式表

| 名称              | 生成多项式                                              | 简记式        |

|-----------------|----------------------------------------------------|------------|

| CRC-4           | $X^4 + X + 1$                                      | 0x03       |

| CRC-8           | $X^8 + X^2 + X + 1$                                | 0x07       |

| CRC-8/MAXIM     | $X^8 + X^5 + X^4 + 1$                              | 0x31       |

| CRC-8/SAE-J1850 | $X^8 + X^4 + X^3 + X^2 + 1$                        | 0x1D       |

| CRC-12          | $X^{12} + X^{11} + X^3 + X^2 + X + 1$              | 0x80F      |

| CRC-16          | $X^{16} + X^{15} + X^2$                            | 0x8005     |

| CRC-CCITT       | $X^{16} + X^{12} + X^5 + 1$                        | 0x1021     |

| CRC-32          | $X^{32} + X^{26} + X^{23} + \dots + X^2 + X + 1$   | 0x04C11DB7 |

| CRC-32C         | $X^{32} + X^{28} + X^{27} + \dots + X^8 + X^6 + 1$ | 0x1EDC6F41 |

## 9 低功耗收发功能 (SLP)

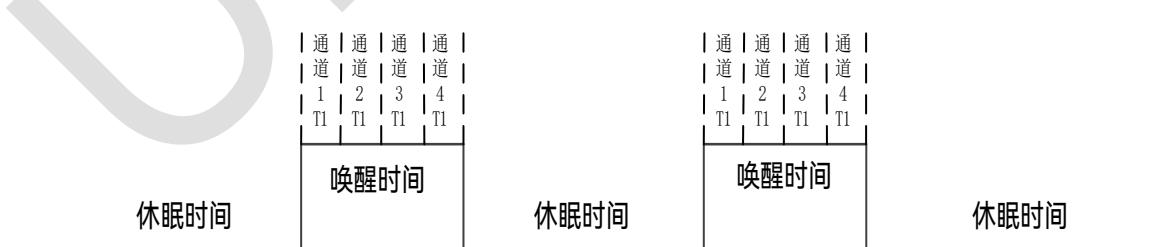

UM2011A可通过配置相关寄存器使芯片的TX和RX工作于Duty Cycle运行模式以节省芯片功耗，并提供了一系列的选项，能够帮助用户在不同的应用需求下实现超低功耗（SLP: Supper Low Power）的发射和接收。同时WOR模式支持最多4个通道的跳频发射和接收，并且在接收模式下，每个通道的载波频率、数据率和滤波器带宽都可以单独配置。

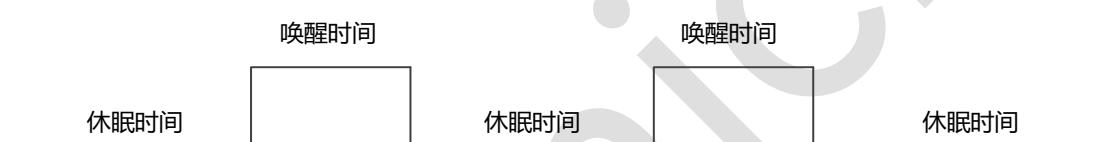

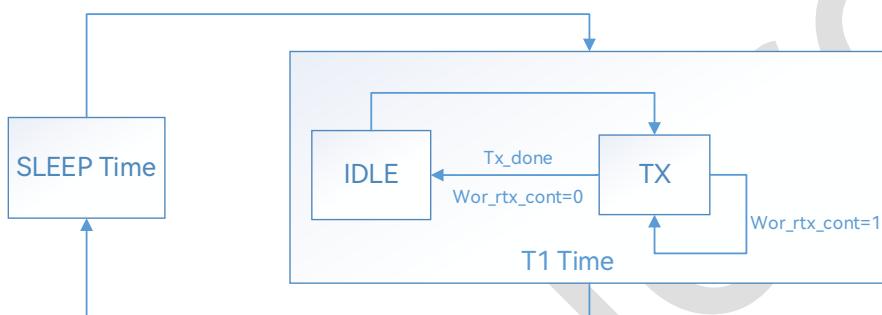

使能 WOR 命令后，芯片在工作状态和 SLEEP 状态之间自动定时切换，WOR 唤醒周期由唤醒计数器 wor\_timer 控制，该计数器的时钟源为 RCL 或 RCL 的分频时钟，其工作流程图如下：

图 9-1: WOR 工作流程图

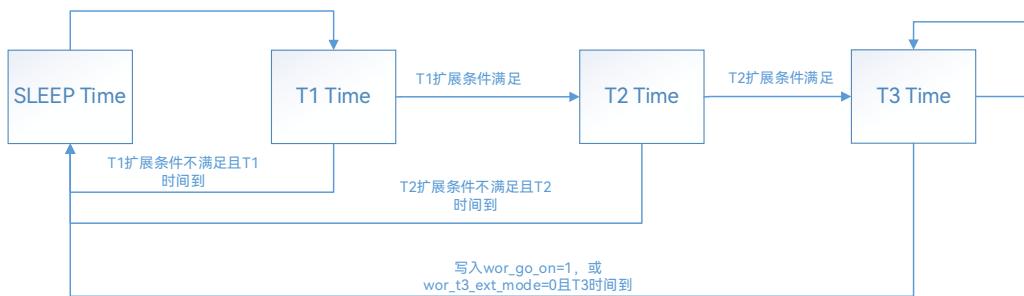

在发射和 IDLE 模式下，唤醒时间是由 T1 时间段组成。在接收模式下，唤醒时间是由 T1、T2、T3 时间段组成，其中 T1 和 T2 的扩展延长条件分别由寄存器 wor\_ext\_sel 和 wor\_t2\_ext\_sel 配置。

时间参数计算公式如下：

$$t = N * 2^{\text{div}} / \text{rcl}$$

其中：N 为寄存器设置值，div 为分频系数，RCL 为低速睡眠时钟，如 RCL=36kHz，div=1，时间 T1 设置 N=0x000A，时间： $t_1 = 0x000A * 2^1 / 36\text{kHz} = 0.555\text{ms}$

注：在 WOR 运行模式，建议不要修改与 WOR 相关的寄存器，如需修改，退出 WOR 模式进入 IDLE 或 Sleep 状态后修改。

表 9-1: WOR 相关寄存器

| 寄存器地址 | 位数  | R/W | 比特名                | 功能说明                                                                                                                                                           |

|-------|-----|-----|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x05  | 6   | R/W | wor_hop_en         | WOR 唤醒后自动跳频使能:<br>0: Disable<br>1: Enable                                                                                                                      |

|       | 5:4 | R/W | wor_hop_max        | WOR 唤醒后自动跳频通道数量，最大 4 个信道，信道频率 $ch_f=ch\_freq+step*index$ 信道号 index 分别由寄存器: ch_index, ch1_freq_num, ch2_freq_num, ch3_freq_num 设置。                              |

| 0x50  | 7:4 | R/W |                    | WOR 多通道模式时，通道 1 的匹配 preamble 长度设置                                                                                                                              |

|       | 3:0 | R/W | preamb_match_len   | 接收 preamble 匹配长度，单位为 bit<br>在 WOR 多通道时<br>preamble_match_len[3:0] 为 ch0 的<br>preamble_len 配置，在非 WOR 多通道时，<br>由 preamble_len_sel 选择加长<br>preamble_match_len 的配置 |

| 0x51  | 7:4 | R/W | ch3_prea_match_len | WOR 多通道模式时，通道 3 的匹配<br>preamble 长度设置                                                                                                                           |

|       | 3:0 | R/W | ch2_prea_match_len | WOR 多通道模式时，通道 2 的匹配<br>preamble 长度设置                                                                                                                           |

| 0x57  | 7:6 | R/W | wor_event_gpio_sel | 选择一个 GPIO 输出 wor_event 信号：<br>00: 不输出<br>01: GPIO0<br>10: GPIO1                                                                                                |

| 0x6D  | 7:0 | R   | wor_ch             | WOR 多通道模式时，当前通道指示                                                                                                                                              |

| 0x74  | 4   | R/W | wor_go_on          | 写 1 继续 WOR 模式，当 wor_ext_mode 为 0，即 WOR 进入 T3 模式后一直保持在 T3 状态，这时如果需要重新进入 WOR 循环，可以对该位写 1，继续启动 WOR                                                                |

| 0x7C  | 7:0 | R/W | command            | 0x88: WOR, WOR 功能开启命令，rcl_en 寄存器需为 1。                                                                                                                          |

| 0xC3  | 7:4 | R/W | wor_rtx_gap[3:0]   | wor_rtx_cont 为 1 时，等待一段时间重新进入发射和接收状态，时间为<br>wor_rtx_gap*40μ s                                                                                                  |

| 寄存器地址 | 位数  | R/W | 比特名                  | 功能说明                                                                                                          |

|-------|-----|-----|----------------------|---------------------------------------------------------------------------------------------------------------|

|       | 3:0 | R/W | wor_clk_sel[3:0]     | WOR 功能计算器时钟分频选择:<br>0000: 1 分频<br>0001: 2 分频<br>0010: 4 分频<br>...<br>1111: 32768 分频                           |

| 0xC4  | 6:5 | R/W | wor_rtx_sel          | WOR 唤醒后工作命令:<br>00/11: IDLE<br>01: RX<br>10: TX                                                               |

|       | 4   | R/W | wor_t3_ext_mode      | T3 期间工作模式, 在 T3 时写 wor_go_on 寄存器为'1'立即进入 sleep:<br>0: T3 时间计数满自动进入 sleep<br>1: 保持在 T3                         |

|       | 3:2 | R/W | wor_t2_ext_sel[1:0]  | 非 0 时, 使能 T2 时间计数:<br>00: T2 扩展不打开, 无 T2 时间<br>01: rssi_pjd_valid<br>10: preamble_match<br>11: syncword_match |

|       | 1:0 | R/W | wor_ext_sel[1:0]     | T1 期间扩展信号选择:<br>00: 不扩展<br>01: rx_rssi_valid<br>10: rssi_pjd_valid<br>11: preamble_match                      |

| 0xC5  | 7:0 | R/W | wor_sleep_time[7:0]  | WOR Sleep 时间:<br>$(1/rcl)*(2^{\text{wor\_clk\_sel}})*\text{wor\_sleep\_time}$                                 |

| 0xC6  | 7:0 | R/W | wor_sleep_time[15:8] | WOR Sleep 时间                                                                                                  |

| 0xC7  | 7:0 | R/W | wor_t1_time[7:0]     | WOR T1 时间:<br>$(1/rcl)*(2^{\text{wor\_clk\_sel}})*\text{wor\_t1\_time}$                                       |

| 0xC8  | 7:0 | R/W | wor_t1_time[15:8]    | WOR T1 时间                                                                                                     |

| 0xC9  | 7:0 | R/W | wor_t2_time[7:0]     | WOR T2 时间:<br>$(1/rcl)*(2^{\text{wor\_clk\_sel}})*\text{wor\_t2\_time}$                                       |

| 0xCA  | 7:0 | R/W | wor_t2_time[15:8]    | WOR T2 时间                                                                                                     |

| 0xCB  | 7:0 | R/W | wor_t3_time[7:0]     | WOR T3 时间:<br>$(1/rcl)*(2^{\text{wor\_clk\_sel}})*\text{wor\_t3\_time}$                                       |

| 0xCC  | 7:0 | R/W | wor_t3_time[15:8]    | WOR T3 时间                                                                                                     |

## 9.1 超低功耗发射模式

在 TX Duty-Cycle 模式下，唤醒状态和睡眠状态定时切换，唤醒时间由 T1 时间段组成，唤醒的时间 T1 和睡眠的时间由寄存器配置固定。唤醒窗口结束后，芯片立即进入睡眠状态，因此数据包的发射时间要低于唤醒时间。数据包发射完成后，芯片默认回到 IDLE 状态，等待唤醒窗口结束再自动切换到睡眠状态。

图 9-2：超低功耗发射流程

操作流程如下：

1. 初始化芯片并进入 IDLE 状态。

2. 写 TXFIFO 数据，写 pw\_fifo\_en=1。

3. 配置调制参数、包模式及帧格式。

4. 启动和校准 RCL。

5. 配置 wor\_sleep\_time 和 wor\_t1\_time，wor\_t1\_time 要大于单包发射时间。

6. 写 wor\_ext\_sel='b00, wor\_t2\_ext\_sel='b00, wor\_rtx\_sel='b10。

7. 写 WOR 命令。

## 9.2 超低功耗接收模式

在 RX Duty-Cycle 模式下，唤醒状态和睡眠状态定时切换，唤醒时间由 T1、T2、T3 时间段组成，唤醒的时间 T1、T2、T3 和睡眠的时间由寄存器配置固定。唤醒窗口结束后，芯片立即进入睡眠状态。SLP 接收的核心是如何让接收机在无信号的时候尽量缩短 RX 的时间，在有信号的时候又

能够恰当地延长 RX 的时间进行接收，最终达到功耗最小化并稳定接收的效果，所以唤醒时间执行 T1 时间后是否需要延长到 T2 或者 T3，可通过 T1 和 T2 的扩展延长条件设置，分别由寄存器 wor\_ext\_sel 和 wor\_t2\_ext\_sel 配置。唤醒监测源分为 rx\_rssi\_valid、rss\_i\_pjd\_valid、Preamble\_match、Syncword\_match。

收到唤醒信号后的唤醒时间和检测源控制如下表：

表 9-2: T1 扩展条件表

| wor_ext_sel | 功能说明                                    | T1 RX 延长条件                                                |

|-------------|-----------------------------------------|-----------------------------------------------------------|

| 00          | 窗口时间为 T1，T1 时间结束后重新进入 SLEEP             | 固定 T1 时间,不延长,<br>wor_ext_sel和wor_ext_sel都必须为 00，可作为定时复位功能 |

| 01          | T1 窗口时间内，如果检测到有效信号，则 RX 进入 T2 或 T3 窗口   | 检测到 rx_rssi_valid 有效                                      |

| 10          | T1 窗口时间内，如果检测到有效信号，则 RX 进入 T2 或 T3 延长窗口 | 检测到 rss_i_pjd_valid 有效                                    |

| 11          | T1 窗口时间内，如果检测到有效信号，则 RX 进入 T2 或 T3 延长窗口 | 检测到 preamble_match 有效                                     |

表 9-3: T2 扩展条件表

| wor_t2_ext_sel | 功能说明                               | T2 RX 延长条件             |

|----------------|------------------------------------|------------------------|

| 00             | 状态机不进入 T2 窗口时间                     |                        |

| 01             | T2 使能，T2 窗口时间内，如果检测到有效信号，则进入 T3 窗口 | 检测到 rss_i_pjd_valid 有效 |

| 10             | T2 使能，T2 窗口时间内，如果检测到有效信号，则进入 T3 窗口 | 检测到 preamble_match 有效  |

| 11             | T2 使能，T2 窗口时间内，如果检测到有效信号，则进入 T3 窗口 | 检测到 syncword_match 有效  |

在 T3 时间结束后，可以由 WOR\_EXT\_MODE 选择重新进入 SLEEP 继续执行 WOR 功能，或者一直停留在 RX。WOR\_EXT\_MODE 为 0 时，T3 结束后自动进入 SLEEP。WOR\_EXT\_MODE 为 1 时，状态机停留在 T3 窗口。在 T3 期间，MCU 可以随时写 wor\_go\_on 寄存器为 1，立即进入 SLEEP，重新进行 WOR 功能。

下面介绍两种基本的 SLP 实现方案：

方案 1：T1、T2 都扩展，T1 扩展信号选择 rx\_rssi\_valid, T2 扩展选择 rss\_i\_pjd\_valid 信号。

图 9-3: SLP 实现方案 1 流程图

操作流程如下：

1. 初始化芯片并进入 IDLE 状态。

2. 配置解调参数、包模式及帧格式。

3. 启动和校准 RCL。

4. 配置 `wor_sleep_time`、`wor_t1_time`、`wor_t2_time` 和 `wor_t3_time`。

5. 写 `wor_ext_sel='b01`, `wor_t2_ext_sel='b01`, `wor_rtx_sel='b01`。

6. 写 `pjd_en='b1`。

7. 写 WOR 命令。

8. 等待 `rx_pkt_done` 中断, 如果芯片进入 T3 并完成一包数据接收, 会给出 `rx_pkt_done` 中断信号。

9. 清 RXFIFO 读指针, 读 RXFIFO 数据。

10. 写 `wor_go_on='b1`, WOR 状态机立即进入 SLEEP, 继续运行 WOR 功能。

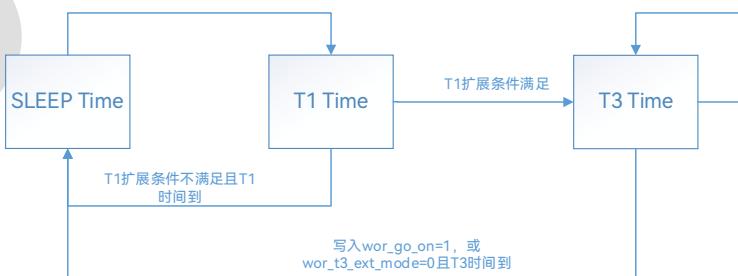

方案 2: T1 扩展, T1 扩展信号选择 `rssi_pjd_valid`; T2 关闭。

图 9-4: SLP 实现方案 2 流程图

操作流程如下：

1. 初始化芯片并进入 IDLE 状态。

2. 配置解调参数、包模式及帧格式。

3. 启动和校准 RCL。

4. 配置 wor\_sleep\_time、wor\_t1\_time、wor\_t2\_time 和 wor\_t3\_time。

5. 写 wor\_ext\_sel='b01, wor\_t2\_ext\_sel='b00, wor\_rtx\_sel='b01。

6. 写 pjd\_en='b1。

7. 设置 RSSI 门限 rx\_rssi\_thr。

8. 写 WOR 命令。

9. 等待 rx\_pkt\_done 中断, 如果芯片进入 T3 并完成一包数据接收, 会给出 rx\_pkt\_done 中断信号。