AN2704

应用笔记

# UM2011A 硬件设计指南

版本: V1.1

广芯微电子（广州）股份有限公司

<http://www.unicmicro.com/>

## 条款协议

本文档的所有部分，其著作产权归广芯微电子（广州）股份有限公司（以下简称广芯微电子）所有，未经广芯微电子授权许可，任何个人及组织不得复制、转载、仿制本文档的全部或部分组件。本文档没有任何形式的担保、立场表达或其他暗示，若有任何因本文档或其中提及的产品所有资讯所引起的直接或间接损失，广芯微电子及所属员工恕不为其担保任何责任。除此以外，本文档所提到的产品规格及资讯仅供参考，内容亦会随时更新，恕不另行通知。

1. 本文档中所记载的关于电路、软件和其他相关信息仅用于说明半导体产品的操作和应用实例。用户如在设备设计中应用本文档中的电路、软件和相关信息，请自行负责。对于用户或第三方因使用上述电路、软件或信息而遭受的任何损失，广芯微电子不承担任何责任。

2. 在准备本文档所记载的信息的过程中，广芯微电子已尽量做到合理注意，但是，广芯微电子并不保证这些信息都是准确无误的。用户因本文档中所记载的信息的错误或遗漏而遭受的任何损失，广芯微电子不承担任何责任。

3. 对于因使用本文档中的广芯微电子产品或技术信息而造成的侵权行为或因此而侵犯第三方的专利、版权或其他知识产权的行为，广芯微电子不承担任何责任。本文档所记载的内容不应视为对广芯微电子或其他人所有的专利、版权或其他知识产权作出任何明示、默示或其它方式的许可及授权。

4. 使用本文档中记载的广芯微电子产品时，应在广芯微电子指定的范围内，特别是在最大额定值、电源工作电压范围、热辐射特性、安装条件以及其他产品特性的范围内使用。对于在上述指定范围之外使用广芯微电子产品而产生的故障或损失，广芯微电子不承担任何责任。

5. 虽然广芯微电子一直致力于提高广芯微电子产品的质量和可靠性，但是，半导体产品有其自身的特点，如一定的故障发生率以及在某些使用条件下会发生故障等。此外，广芯微电子产品均未进行防辐射设计。所以请采取安全保护措施，以避免当广芯微电子产品在发生故障而造成火灾时导致人身事故、伤害或损害的事故。例如进行软硬件安全设计（包括但不限于冗余设计、防火控制以及故障预防等）、适当的老化处理或其他适当的措施等。

# 目录

|     |         |   |

|-----|---------|---|

| 1   | 概述      | 1 |

| 2   | 应用参考原理图 | 2 |

| 2.1 | 参考电路概述  | 3 |

| 2.2 | 物料清单    | 4 |

| 3   | 硬件设计    | 6 |

| 4   | 版本修订    | 8 |

# 1 概述

本文档是 UM2011A 应用开发指南，主要阐述如何设计和应用 UM2011A 原理图和 PCB 版图，以达到最佳的射频性能。

Unichmicro

## 2 应用参考原理图

直连匹配电路无需 RF 开关, TX 和 RX 通过阻抗变换后直连到天线。直连匹配优化了电路结构, 采用较少的元件, 既可满足 CE/FCC 等无线规范要求, 又可实现高接收灵敏度、高效率和大功率输出。

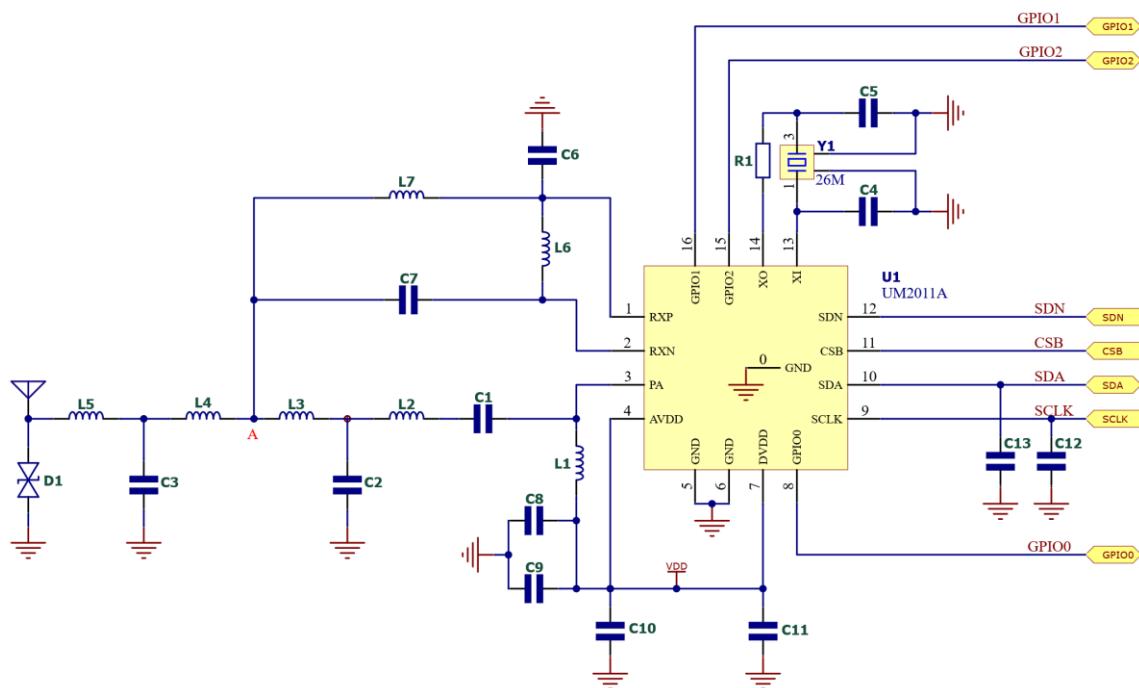

图 2-1: 典型应用参考原理图

说明:

1. SDN 为芯片关断功能脚, 高电平关断。如果该引脚受 MCU 控制, 必须给固定电平。如果应用中不需要关断功能, 可以将 SDN 脚接地。

2. 芯片关断时, SDN、GPIO0、GPIO1、GPIO2、SCLK 和 SDA 处于高阻状态, CSB 内部自带  $100\text{k}\Omega$  上拉。

3. 芯片睡眠时, SDN、SCLK、CSB、SDA 为输入状态 (除了 CSB 脚, 其它脚都不带上拉或下拉), GPIO0、GPIO1、GPIO2 方向保持, 若为输出状态, 则输出低电平。

## 2.1 参考电路概述

1. L1 是扼流电感。

2. C8~C11 是电源退耦电容，用于减少 PA 输出对电源的影响。根据实际应用需求要做适当调整。

3. C1 是隔直电容，并且与 L2 的部分电感在工作频点形成谐振起到谐波抑制作用。

4. 上图标识的 A 点为直连点，该点阻抗是  $50\Omega$ 。

5. L2、C2 和 L3 组成 TX 匹配网络，实现 PA 输出和直连点阻抗匹配。

6. C6、L6、C7 和 L7 组成 RX Balun 匹配网络，实现接收机的输入阻抗和直连点匹配，并使得接收信号到达差分输入口 RFIP 和 RFIN 处时幅度相等，相位相差 180 度。

7. L4、C3、L5 为  $50\Omega$  到  $50\Omega$  的 T 型低通滤波匹配网络。

8. Y1 推荐用频率容差 $\pm 10\text{ppm}$  的 26MHz 晶体，可接受的晶体频率容差取决于用户产品通讯系统的要求，如频率、信道、带宽等。

9. C4、C5 为晶体负载电容（注意芯片内部已经集成了约  $4\text{pF}$  的负载电容，以  $C_L=15\text{pF}$  的 26MHz 晶体为例，折合晶体相连走线分布电容  $2\text{pF}$ ，C4 和 C5 取值约为  $15*2-4-2=24\text{pF}$ ）。

10. C12/C13 为滤波电容，在布线不合理或走线太长情况下，可以酌情添加以提升抗干扰能力，推荐值为  $27\text{pF}$ 。

11. D1 为预留 ESD 保护管，在某些容易接触到静电的应用场景，需要根据需求增加 ESD 保护，确保芯片在使用过程中不容易被 ESD 损伤到。

12. 数字功能引脚（GPIO0/GPIO1/GPIO2/SDN/CSB/SCK/SDA）如果需要引出到外部，建议串连  $560\Omega$  电阻以提升 ESD 防护能力。

## 2.2 物料清单

表 2-1: 13dBm 典型应用物料清单

| 位号  | 描述                              | 元件值 |     |     | 单位  |

|-----|---------------------------------|-----|-----|-----|-----|

|     |                                 | 433 | 868 | 915 |     |

| C1  | ±5%, 0603, NP0, 50V, YAGEO      | 6.8 | 10  | 10  | pF  |

| C2  | ±5%, 0603, NP0, 50V, YAGEO      | 6.2 | 5   | 5   | pF  |

| C3  | ±5%, 0603, NP0, 50V, YAGEO      | 6.2 | 3.6 | 3.6 | pF  |

| C4  | ±5%, 0402, NP0, 50V, YAGEO      | 24  | 24  | 24  | pF  |

| C5  | ±5%, 0402, NP0, 50V, YAGEO      | 24  | 24  | 24  | pF  |

| C6  | ±5%, 0603, NP0, 50V, YAGEO      | 3.9 | 2   | 2   | pF  |

| C7  | ±5%, 0603, NP0, 50V, YAGEO      | 2   | 2   | 2   | pF  |

| C8  | ±10%, 0603, X5R, 25V, YAGEO     | 4.7 | 4.7 | 4.7 | μF  |

| C9  | ±5%, 0603 NP0, 50V, YAGEO       | 470 | 470 | 470 | pF  |

| C10 | ±10%, 0402, X7R, 50V, YAGEO     | 0.1 | 0.1 | 0.1 | μF  |

| C11 | ±10%, 0402, X7R, 50V, SAMSUNG   | 0.1 | 0.1 | 0.1 | μF  |

| L1  | ±5%, 0603, 贴片电感, Sunlord        | 180 | 100 | 100 | nH  |

| L2  | ±5%, 0603, 贴片电感, Sunlord        | 56  | 12  | 12  | nH  |

| L3  | ±5%, 0603, 贴片电感, Sunlord        | 33  | 4.7 | 4.7 | nH  |

| L4  | ±5%, 0603, 贴片电感, Sunlord        | 22  | 10  | 10  | nH  |

| L5  | ±5%, 0603, 贴片电感, Sunlord        | 22  | 10  | 10  | nH  |

| L6  | ±5%, 0603, 贴片电感, Sunlord        | 47  | 10  | 10  | nH  |

| L7  | ±5%, 0603, 贴片电感, Sunlord        | 82  | 22  | 22  | nH  |

| R1  | ±1%, 0402, 贴片电阻, UNI-ROYAL      | 330 | 330 | 330 | Ω   |

| Y1  | 3225 无源晶振 26MHz, 10ppm, 15pF 负载 | 26  | 26  | 26  | MHz |

表 2-2: 20dBm 典型应用物料清单

| 位号 | 描述                         | 元件值 |     |     | 单位 |

|----|----------------------------|-----|-----|-----|----|

|    |                            | 433 | 868 | 915 |    |

| C1 | ±5%, 0603, NP0, 50V, YAGEO | 8.2 | 6   | 3.9 | pF |

| C2 | ±5%, 0603, NP0, 50V, YAGEO | 7.5 | 3.3 | 3.3 | pF |

| C3 | ±5%, 0603, NP0, 50V, YAGEO | 6.8 | 3.9 | 3.9 | pF |

| C4 | ±1%, 0402, NP0, 50V, YAGEO | 24  | 24  | 24  | pF |

| C5 | ±1%, 0402, NP0, 50V, YAGEO | 24  | 24  | 24  | pF |

| C6 | ±5%, 0603, NP0, 50V, YAGEO | 3.9 | 2.7 | 2.7 | pF |

| 位号  | 描述                                   | 元件值       |     |     | 单位       |

|-----|--------------------------------------|-----------|-----|-----|----------|

|     |                                      | 433       | 868 | 915 |          |

| C7  | $\pm 5\%$ , 0603, NP0, 50V, YAGEO    | 2         | 2   | 2   | pF       |

| C8  | $\pm 10\%$ , 0603, X5R, 25V, YAGEO   | 4.7       | 4.7 | 4.7 | $\mu$ F  |

| C9  | $\pm 5\%$ , 0603 NP0, 50 V, YAGEO    | 470       | 470 | 470 | pF       |

| C10 | $\pm 10\%$ , 0402, X7R, 50V, YAGEO   | 0.1       | 0.1 | 0.1 | $\mu$ F  |

| C11 | $\pm 10\%$ , 0402, X7R, 50V, SAMSUNG | 0.1       | 0.1 | 0.1 | $\mu$ F  |

| L1  | $\pm 5\%$ , 0603, 贴片电感, Sunlord      | 180       | 100 | 100 | nH       |

| L2  | $\pm 5\%$ , 0603, 贴片电感, Sunlord      | 22        | 15  | 15  | nH       |

| L3  | $\pm 5\%$ , 0603                     | 18pF (电容) | 18  | 18  | nH       |

| L4  | $\pm 5\%$ , 0603, 贴片电感, Sunlord      | 33        | 8.2 | 8.2 | nH       |

| L5  | $\pm 5\%$ , 0603, 贴片电感, Sunlord      | 27        | 8.2 | 8.2 | nH       |

| L6  | $\pm 5\%$ , 0603, 贴片电感, Sunlord      | 47        | 10  | 10  | nH       |

| L7  | $\pm 5\%$ , 0603, 贴片电感, Sunlord      | 82        | 22  | 22  | nH       |

| R1  | $\pm 1\%$ , 0402, 贴片电阻, UNI-ROYAL    | 330       | 330 | 330 | $\Omega$ |

| Y1  | 3225 无源晶振 26MHz, 10ppm, 15pF 负载      | 26        | 26  | 26  | MHz      |

### 3 硬件设计

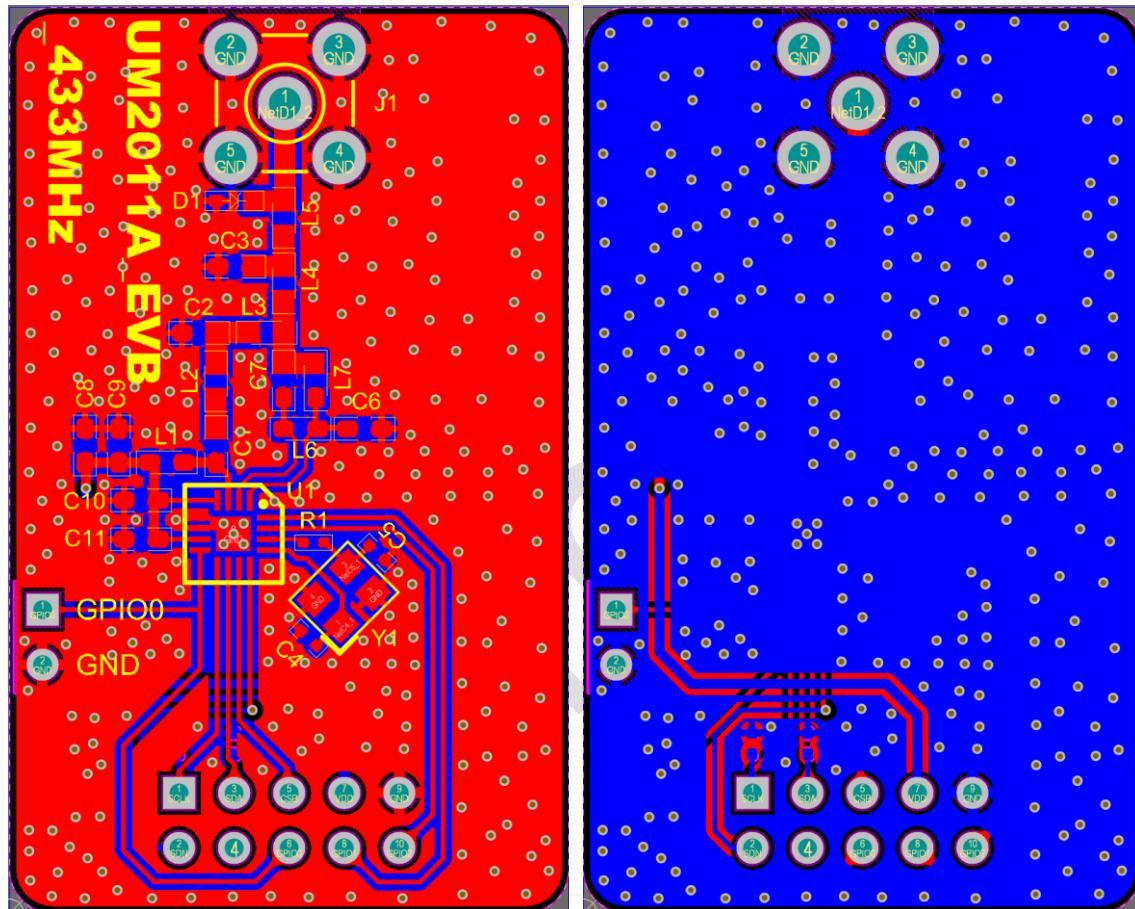

本文档以 UM2011A\_EVB 的 PCB 为例来阐述应用设计的注意事项。图 3-1 中 PCB 采用 2 层板设计。

图 3-1: PCB Layout 应用参考

说明如下：

1. 射频信号路径尽量的直且短，减小射频信号输入与输出的损耗。

2. 射频走线应该尽量平整，以减小传输线上的阻抗波动而产生反射。在上图中 L2 到 J1 间走线为  $50\Omega$  阻抗传输线。实际设计中根据实际板厚以及 PCB 材质，计算合适的线宽和传输线和地的间隙宽度，以期得到较为准确的  $50\Omega$  阻抗。以 1mm 板厚双面板为例，铜厚 1oz，线宽 1mm，传输线到地间距 0.254，这样就可以得到阻抗在 50 欧姆的传输线。

3. Choke 电感 L1 离 PA 管脚尽量近。相邻电感尽量正交摆放，可减少相互耦合。

4. 射频芯片和匹配电路部分要铺地，并确保匹配电路两侧完整包地，匹配电路对应的底层要完整铺地，不要被走线穿插分割。接收和发射匹配电路之间的地要保留，此地面积尽量大一些，并打过孔加强接地。IC 的下方相邻层要有完整的铺地（GND），IC 下方的焊盘要打过孔跟底层相连，增强芯片的接地。

5. 晶振走线尽可能短，晶振周围保持良好接地面，走线尽量不要从晶振下方穿过。

unicmicro

## 4 版本修订

| 版本   | 日期         | 描述      |

|------|------------|---------|

| V1.0 | 2025.10.15 | 初始版     |

| V1.1 | 2025.12.05 | 优化匹配参数。 |

|      |            |         |

|      |            |         |