**高性能低功耗 32 位微控制器：ARM®Cortex®-M4 (FPU+DSP)、512KB eFlash、

160KB+4KB+32KB SRAM、USB FS、千兆以太网、加解密引擎、19 个定时器、RTC、

2 个 ADC、2 个 DAC、多个通信接口和摄像头接口**

## 产品特性

### ● 低功耗电源管理系统

- 2μA @3.0V Standby 模式， RTC 工作

- 99μA/MHz @3.0V @204MHz Run 模式

- 集成 RTC、LPTIM、IWDT、LPUART

- 睡眠（Sleep）、停机（Stop）、待机（Standby）和深度待机（DeepStandby）模式

- VBAT 为 RTC 和 20×32 位备份寄存器 + 可选 4KB 备份 SRAM 供电

LQFP100 (14\*14mm)

LQFP64 (10\*10mm)

### ● 处理器

- 32 位 ARM Cortex-M4

- 内置 FPU (单精度浮点运算单元)

- 内置硬件 DSP 指令单元

- 支持内存保护单元 (MPU)

- 三级流水线，系统最高主频 204MHz (240MHz@boost mode)

- 单周期硬件乘法器

- 内置硬件除法器

- CPU 运算性能达到 333DMIPS (1.39DMIPS/MHz, 240MHz)

- CoreMark 跑分可高达 826 分 (3.445CoreMark/MHz, 240MHz)

- 4KB 指令 Cache 和 256-byte 数据 Cache, 支持 0 等待周期取指

### ● 存储器

- 160KB SRAM

- 32KB DMA SRAM

- 4KB Retention SRAM

- 512KB eFlash

### ● 通用 I/O

- 多达 82 个具有中断功能的 I/O 端口

- 多达 58 个具有 5V 耐压的 I/O

### ● 复位和电源管理

- 上电复位 (POR)、掉电复位 (PDR)、低电压检测 (LVD) 和欠压复位 (BOR)

### ● 时钟

- 1MHz 到 48MHz 晶振

- 内置 48MHz RC 振荡器

- 带校准功能的 32.768kHz 晶振

- 内置低频的 32kHz RC 振荡器

- 2 个 PLL (支持整数、小数、扩频功能)，其中一个是音频 PLL

### ● 通信接口

- 最大 6 个 UART 接口 (支持 7/8/9 数据位，最高支持 10.5Mbps)，支持 IrDA 控制

- 最大 2 个 USART 接口，支持 UART/SPI/IrDA/LIN 控制

- 1 个低功耗串口 (LPUART)

- 3 个 I2C 接口 (最高支持 1 Mbps)，支持 SMBus

- 2 个 I2S 接口 (支持 I2S/PCM 格式)

- 最大 4 个通用的 SPI 接口 (最高支持 60MHz)

- 最大 1 个 QSPI 接口 (最高支持 102MHz)

- 最多支持 50 路 PWM (6 对死区互补) 输出

- 2 个 CAN 工业总线，支持 CAN2.0B (最高速率 1 Mbps)

- 1 个 48MHz 的 SDIO/SD/eMMC 接口

- 模拟外设

- 2 个 12 位最高采样率 5.25Msps 的 A/D 转换器，多达 16 个通道，支持单端和差分输入

- 2 个 12 位 1Msps D/A 转换器，带 Buffer

- 2 个运算放大器 (OPA)，支持单端 PGA 和比较器功能

- 最大 3 个模拟比较器 (ACMP)

- 内置 1.5/2.0/2.5/3V 参考电压源 (VREF)

- 内置温度传感器 (TS)

- 定时器

- 2 个 32 位高性能计时器 (eQCT™: TIM0/TIM7) , 每个定时器支持 4 路输入捕获, 3 对+1 路 PWM 输出, 3 对死区互补, 支持刹车功能。支持系统时钟 2 倍频的 PWM 精度, 最高 2.08ns (480MHz) ; 支持增量正交编码器和霍尔传感器

- 10 个 32 位通用定时器 (TIM1/TIM2/TIM3/TIM4/TIM8/TIM9/TIM10/TIM11/TIM12/TIM13) , 每个定时器支持 4 路输入捕获, 4 路 PWM 输出。支持系统时钟 2 倍频的 PWM 精度, 最高 2.08ns (480MHz) ; 支持增量正交编码器和霍尔传感器

- 2 个 32 位基本定时器 (TIM5/TIM6) , 可触发 D/A 转换输出

- 2 个 16 位低功耗定时器 (LPTIM0/LPTIM1) , 每个定时器支持 1 路 PWM 输出

- 1 个低功耗看门狗定时器 IWDT, 可复位/中断

- 1 个窗口看门狗定时器 WWDT

- 1 个 24 位 Systick 定时器

- 实时时钟 (RTC)

- 支持硬件万年历 (秒、分钟、小时、星期几、日期、月份和年份显示) , 支持校准功能

- 高速接口

- 1 个自带 DMA 的 10M/100M/1000M 以太网控制器 (RGMII/RMII/MII 接口)

- 1 个 USB 接口, 支持全速 USB FS Device 接口 (内置 PHY)

- 摄像头和显示接口

- LCD 并行接口, 兼容 8080 模式

- 8 位到 14 位的数字并行摄像头接口 (DCMI 接口) , 传输率高达 54MB/s

- 硬件加速运算协处理器

- Cordic 加速器 (sin、cos、arctan、平方根、乘法、除法等)

- 硬件加解密引擎

- 硬件加解密: 用于 AES(128/256) 和 SHA256

- 随机数发生器

- CRC 计算单元

- 安全

- 防抄板设计, 防止 eFlash 中程序被窃取

- code CRC16-CCITT/CRC32 数据校验算法

- 硬件加速

- 128 位全球唯一芯片序列号 ID

- 电气参数

- 工作电压: 1.8 ~ 3.6V

- 工作温度: -40 ~ 105°C

- 湿敏等级: MSL-3

- 开发支持

- 内置 Boot 引导程序, 支持 USB/UART 下载, 支持 ISP 和 IAP 应用程序更新

- JTAG->SWD 模式在线调试/下载

- 完整 SDK 开发包、EVB 硬件开发套件

- 选型

| 类型          | 型号                                                                       |

|-------------|--------------------------------------------------------------------------|

| 512KB Flash | UM3241F-VCT6 (LQFP100)<br>UM3241F-RCT6 (LQFP64)<br>UM3242F-RET6 (LQFP64) |

# 目录

|                                |    |

|--------------------------------|----|

| 1 产品简介 .....                   | 1  |

| 1.1 功能框图 .....                 | 2  |

| 1.2 资源配置表 .....                | 3  |

| 2 功能简介 .....                   | 5  |

| 2.1 处理器内核 .....                | 5  |

| 2.2 硬件存储加速器 .....              | 5  |

| 2.3 存储器 .....                  | 5  |

| 2.3.1 嵌入式 FLASH .....          | 5  |

| 2.3.2 嵌入式 SRAM .....           | 6  |

| 2.4 嵌套的向量式中断控制器 (NVIC) .....   | 6  |

| 2.5 时钟架构 (Clock) .....         | 7  |

| 2.6 复位 (Reset) .....           | 8  |

| 2.7 电源和电源管理 (PMU) .....        | 9  |

| 2.8 启动模式 .....                 | 11 |

| 2.9 DMA 控制器 (DMA) .....        | 11 |

| 2.10 通用异步收发器接口 (UART) .....    | 12 |

| 2.11 通用同步/异步收发器 (USART) .....  | 12 |

| 2.12 低功耗串口 (LPUART) .....      | 14 |

| 2.13 通用输入输出接口 (GPIO) .....     | 15 |

| 2.14 定时器/计数器 (TIMx) .....      | 15 |

| 2.15 低功耗定时器 (LPTIM) .....      | 16 |

| 2.16 I2C 接口 (I2C) .....        | 17 |

| 2.17 实时时钟 (RTC) .....          | 17 |

| 2.18 串行音频接口 (I2S) .....        | 17 |

| 2.19 控制器局域网络 (CAN) .....       | 18 |

| 2.20 同步串行接口 (SPI) .....        | 19 |

| 2.21 四线 SPI 控制器 (QSPI) .....   | 20 |

| 2.22 独立看门狗 (IWDT) .....        | 21 |

| 2.23 窗口看门狗 (WWDT) .....        | 21 |

| 2.24 硬件加速运算协处理器 (Cordic) ..... | 22 |

| 2.25 安全数字输入输出接口 (SDIO) .....   | 22 |

| 2.26 数字摄像头接口 (DCMI) .....      | 23 |

| 2.27 外部存储接口 (EMC) .....        | 23 |

| 2.28 以太网接口 (EMAC) .....        | 24 |

| 2.29 随机数 (RNG) .....           | 24 |

| 2.30 高级加解密算法加速器 (AES) .....    | 25 |

|         |                              |    |

|---------|------------------------------|----|

| 2.31    | 安全散列算法加速器 (SHA) .....        | 25 |

| 2.32    | USB FS Device 接口 (USB) ..... | 26 |

| 2.33    | 模拟/数字转换器 (ADC) .....         | 26 |

| 2.34    | 数字/模拟转换器 (DAC) .....         | 27 |

| 2.35    | 运算放大器 (OPA) .....            | 28 |

| 2.36    | 模拟比较器 (ACMP) .....           | 28 |

| 2.37    | 温度传感器 (TS) .....             | 28 |

| 2.38    | 安全系统 .....                   | 28 |

| 2.38.1  | 唯一 ID 号 .....                | 28 |

| 2.38.2  | CRC16/32 硬件循环冗余校验码 .....     | 29 |

| 2.39    | 调试和编程系统 .....                | 29 |

| 3       | 引脚定义和描述 .....                | 30 |

| 3.1     | 引脚定义 .....                   | 30 |

| 3.2     | 引脚描述 .....                   | 32 |

| 3.3     | 引脚复用定义 .....                 | 46 |

| 4       | 电气特性 .....                   | 51 |

| 4.1     | 测试条件 .....                   | 51 |

| 4.1.1   | 最大值和最小值 .....                | 51 |

| 4.1.2   | 典型值 .....                    | 51 |

| 4.1.3   | 典型曲线 .....                   | 51 |

| 4.1.4   | 供电方案 .....                   | 51 |

| 4.2     | 绝对最大额定值 .....                | 52 |

| 4.3     | 工作条件 .....                   | 53 |

| 4.3.1   | 通用工作条件 .....                 | 53 |

| 4.3.2   | 上电和掉电时的工作条件 .....            | 54 |

| 4.3.3   | 内嵌复位和电源控制模块特性 .....          | 54 |

| 4.3.4   | 内置参考电压 .....                 | 56 |

| 4.3.5   | 供电电流特性 .....                 | 56 |

| 4.3.6   | 外部时钟源特性 .....                | 59 |

| 4.3.6.1 | 外部高速时钟源 (HSE/XTH) .....      | 59 |

| 4.3.6.2 | 外部低速时钟源 (LSE/XTL) .....      | 60 |

| 4.3.7   | 内部时钟源特性 .....                | 60 |

| 4.3.7.1 | 高速内部 RC 振荡器 (RCH) .....      | 60 |

| 4.3.7.2 | 低速内部 RC 振荡器 (RCL) .....      | 60 |

| 4.3.8   | 从低功耗模式唤醒的时间 .....            | 61 |

| 4.3.9   | PLL 特性 .....                 | 61 |

| 4.3.10  | FLASH 存储器特性 .....            | 62 |

| 4.3.11  | 绝对最大额定值 (电气敏感性) .....        | 62 |

|          |                         |    |

|----------|-------------------------|----|

| 4.3.11.1 | 静态闩锁(LU) .....          | 62 |

| 4.3.12   | I/O 端口特性 .....          | 62 |

| 4.3.13   | ADC 电气特性 .....          | 63 |

| 4.3.14   | DAC 电气特性 .....          | 64 |

| 4.3.15   | 运算放大器 (OPA) 电气特性 .....  | 64 |

| 4.3.16   | 模拟比较器 (ACMP) 电气特性 ..... | 65 |

| 4.3.17   | 温度传感器 (TS) 特性 .....     | 65 |

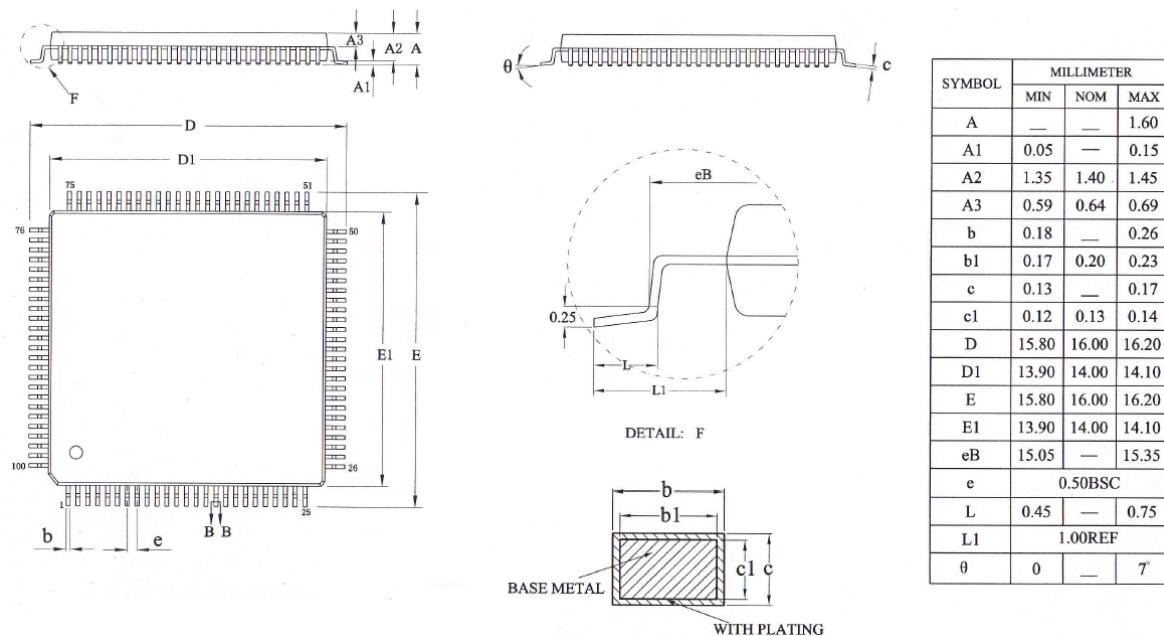

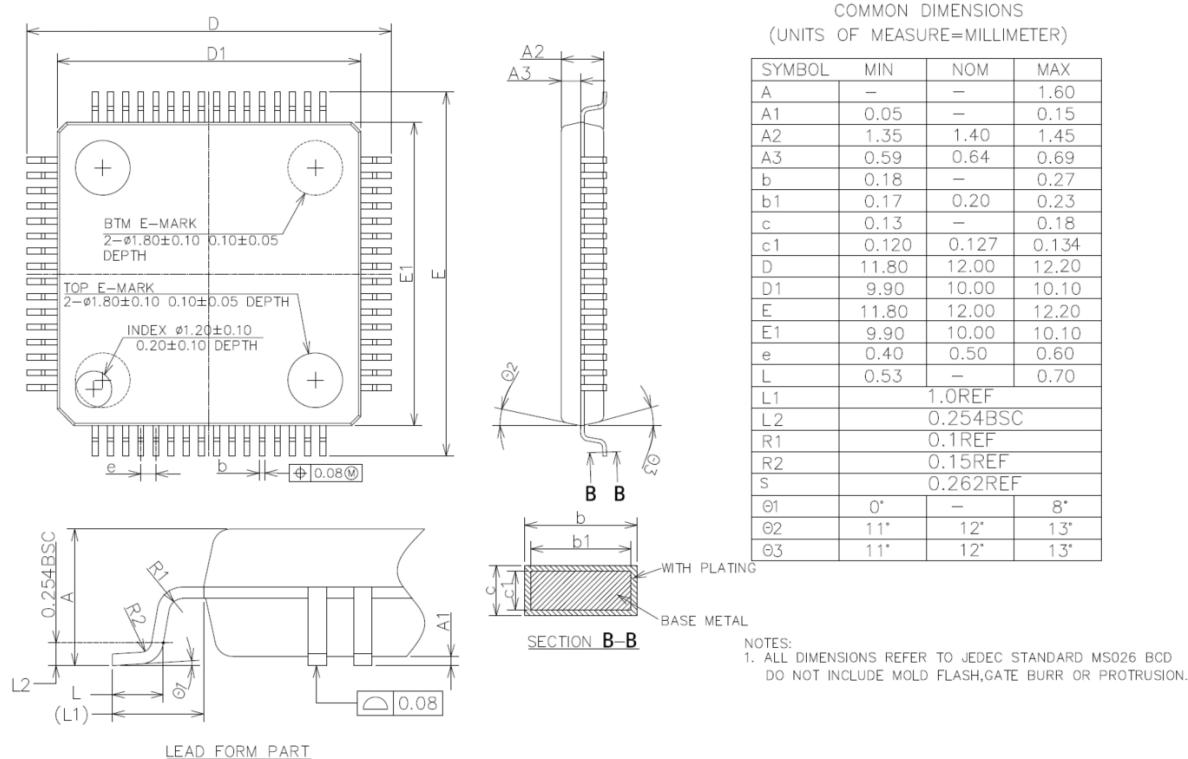

| 5        | 封装尺寸 .....              | 66 |

| 5.1      | LQFP100 (14*14mm) ..... | 66 |

| 5.2      | LQFP64 (10*10mm) .....  | 67 |

| 6        | 版本维护 .....              | 68 |

| 7        | 联系我们 .....              | 69 |

# 1 产品简介

UM324xF 系列芯片是高性能低功耗的 ARM® Cortex® -M4 核的通用微处理器芯片。其中，M4 处理器核支持 DSP 指令集，有浮点运算单元（FPU）、内存保护单元（MPU）。系统典型工作时钟频率 204MHz（240MHz @boost mode）。内置 FLASH 最大容量为 512KB，SRAM 最大容量为 160KB，DMA SRAM 容量为 32KB。支持 1.8 ~ 3.6V 宽电压供电，适宜在-40°C至 105°C（工业级）的温度下工作。

UM324xF 系列芯片带有丰富外设，包括 1 个 USB FS Device 接口、1 个 SDIO/SD/eMMC 接口、1 个 10/100M/1000M 以太网接口、1 个外部高速存储接口（EMC）、2 个 12 位的高速 ADC、2 个 12 位的 DAC、内置温度传感器、3 个比较器、2 个运算放大器、2 个 USART、6 个 UART、4 个 SPI 接口、3 个 I2C 接口、2 个 I2S 接口、2 个看门狗定时器、2 个 CAN 总线接口、1 个 QSPI 接口、14 个计数器/定时器（高级控制器和通用定时器）、1 个低功耗串口（LPUART）、2 个低功耗计时器（LPTIMx）、1 个 32 位 RTC 时钟及计数器、高达 82 通道的通用输入输出口、支持数字摄像头接口（DCMI）和 I8080 LCD 显示接口、同时集成硬件 Cordic 模块（支持 sin、cos、arctan、平方根、乘除法等）、内建加解密引擎（包含 AES、SHA 等）、1 个可产生随机 Key 的随机数产生器（RNG）。

## 适用场景：

- 电机应用

- 二维码识别

- 智能门锁

- 网关

- 打印机

- 物联网应用等

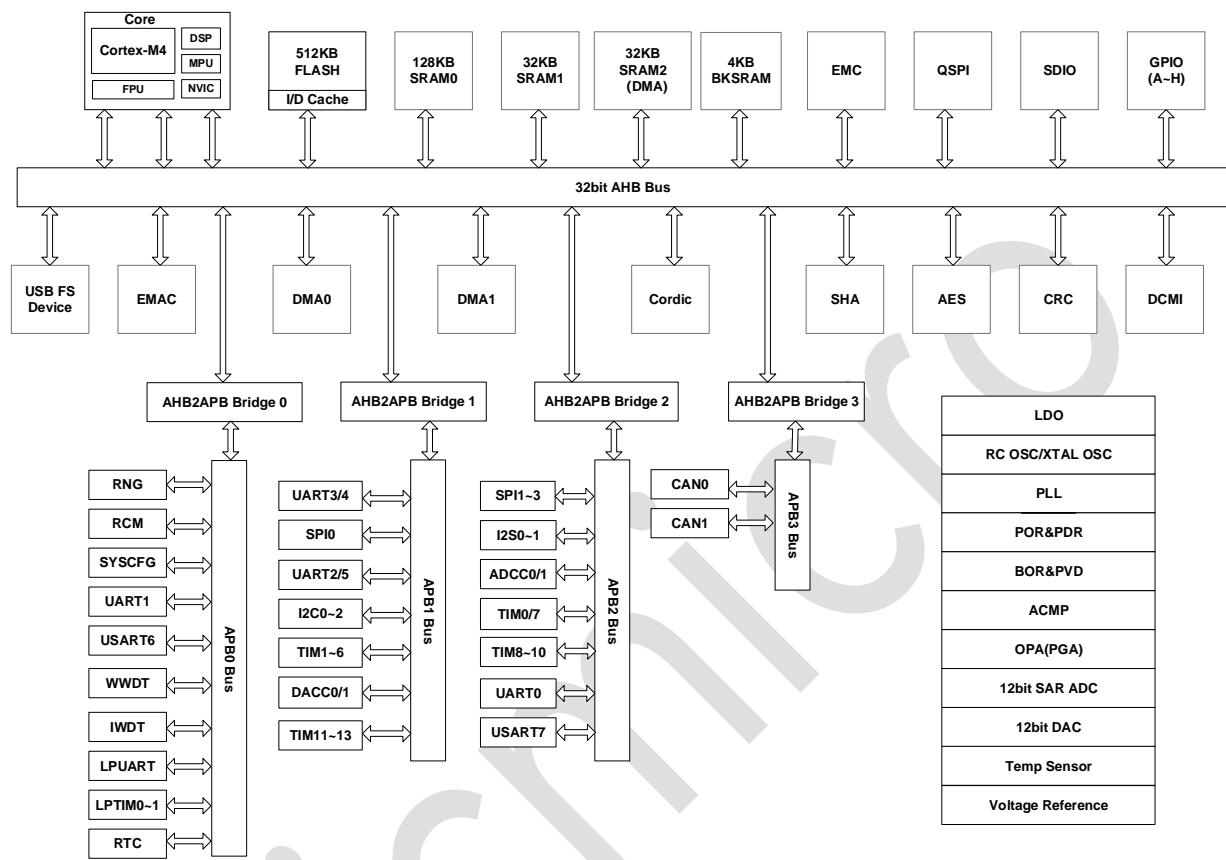

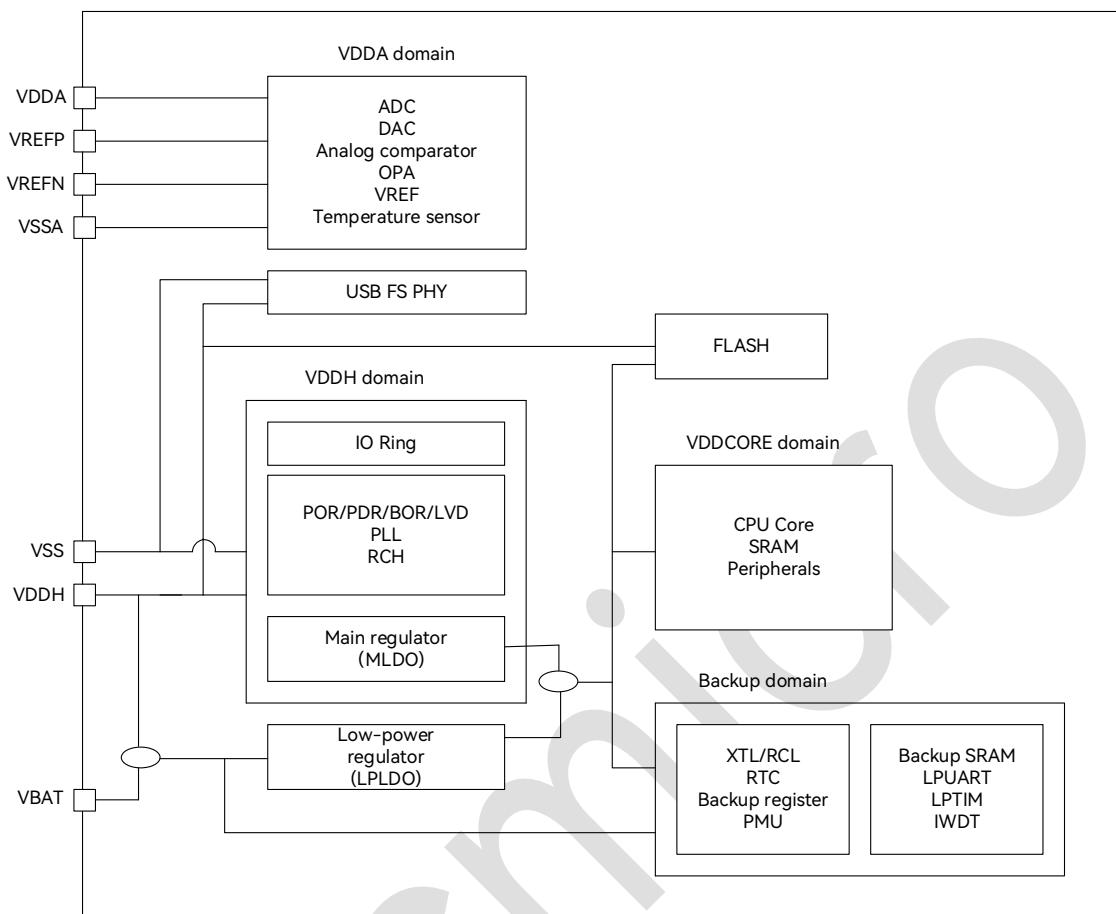

## 1.1 功能框图

图 1-1: 功能框图

## 1.2 资源配置表

表 1-1: 资源配置表

| 型号             |                   | UM3241F-RCT6 | UM3242F-RET6 | UM3241F-VCT6 |

|----------------|-------------------|--------------|--------------|--------------|

| Flash (KB)     |                   | 512          |              |              |

| SRAM (KB)      | 系统                | 160 (128+32) |              |              |

|                | 备份 (Backup)       | 4            |              |              |

| DMA SRAM (KB)  |                   | 32           |              |              |

| 定时器            | 通用定时器             | 10 (32 bits) |              |              |

|                | 高级控制定时器           | 2 (32 bits)  |              |              |

|                | 基本定时器             | 2 (32 bits)  |              |              |

|                | SysTick           | 有            |              |              |

|                | IWDT              | 有            |              |              |

|                | WWDT              | 有            |              |              |

|                | LPTIM             | 2            |              |              |

|                | PWM Channels      | 36           | 36           | 50           |

| 通信接口           | SPI               | 3            | 3            | 4            |

|                | I2S               | 2            |              |              |

|                | I2C               | 3            |              |              |

|                | USART             | 2            |              |              |

|                | UART              | 5            | 5            | 6            |

|                | LPUART            | 1            |              |              |

|                | CAN (2.0B)        | 2            |              |              |

|                | USB FS Device     | 1            |              |              |

|                | SDIO              | 1            |              |              |

|                | QSPI              | 无            | 无            | 1            |

| 以太网            |                   | GbE/FE       |              |              |

| RTC            |                   | 1            |              |              |

| 相机接口 (DCMI)    |                   | 1            |              |              |

| I8080 接口 (LCD) |                   | 无            | 无            | 1            |

| EMC            |                   | 无            | 无            | 1            |

| GPIO           |                   | 51           | 51           | 82           |

| 模拟             | 12 位 ADC Channels | 2            |              |              |

|                |                   | 16           |              |              |

| 型号                                              | UM3241F-RCT6                     | UM3242F-RET6       | UM3241F-VCT6 |

|-------------------------------------------------|----------------------------------|--------------------|--------------|

| 12 位 DAC<br>Channels                            |                                  | 2<br>2             |              |

| Internal Voltage<br>Reference<br>(1.5/2/2.5/3V) | No                               |                    | Yes          |

| OPA (PGA)                                       |                                  | 2                  |              |

| ACMP                                            |                                  | 3                  |              |

| TS                                              |                                  | 有                  |              |

| Cordic 算法模块                                     |                                  | 1                  |              |

| 硬件加解密<br>引擎                                     | CRC                              | 有                  |              |

|                                                 | AES (256)                        | 有                  |              |

|                                                 | SHA (256)                        | 有                  |              |

|                                                 | 随机数发生器                           | 有                  |              |

| 最大 CPU 频率                                       | 204MHz (240MHz @ boost mode)     |                    |              |

| 工作电压                                            | 1.8 到 3.6V                       |                    |              |

| 工作温度                                            | 环境温度: -40 至 +85°C / -40 至 +105°C |                    |              |

|                                                 | 结温: -40 至 +125°C                 |                    |              |

| 封装                                              | LQFP64 (10*10 mm)                | LQFP100 (14*14 mm) |              |

## 2 功能简介

### 2.1 处理器内核

集成了最新一代嵌入式 ARM Cortex™-M4F 处理器，在 Cortex™-M3 内核的基础上强化了运算能力、新增加了浮点运算处理单元（FPU）、DSP 和并行计算指令，提供 1.39DMIPS/MHz 的优异性能。同时其高效的信号处理能力与 Cortex-M 系列处理器的低功耗，低成本和易于使用的优点组合，用以满足需要控制和信号处理混合能力且易于使用的应用场景。

ARM Cortex™-M4F 32 位精简指令集处理器具有优异的代码效率。

### 2.2 硬件存储加速器

针对工业标准 ARM® Cortex™-M4F 处理器优化的存储器加速器，内置 4KB 指令 Cache 和 256-byte 数据 Cache，对于传统的 FLASH 技术而言，通常高速的 MCU 需要等待低速的 FLASH，从而影响性能。而此加速器很好地平衡了 ARM Cortex - M4F 与 FLASH 之间的性能差异。根据测试，凭借此加速器所获得的性能相当于 Flash 在 CPU 频率高达 240MHz 时以 0 个等待周期执行程序。

### 2.3 存储器

芯片包含嵌入式 FLASH 和嵌入式 SRAM。

#### 2.3.1 嵌入式 FLASH

内置一个 512KB 的 eFlash，用于存储程序和数据。

### 2.3.2 嵌入式 SRAM

主要特性:

- 多达 160KB 的系统 SRAM，其中包括 128KB 的 SRAM0，CPU 能以 0 等待周期访问。

- 4KB 的备份 SRAM

- DMA 专用的 32KB 的 DMA SRAM，支持 CPU 和 DMA 写操作，但只支持 DMA 读操作

## 2.4 嵌套的向量式中断控制器 (NVIC)

内置嵌套的向量式中断控制器，能够处理多个可屏蔽中断通道（不包括 16 个 Cortex™-M4F 的中断线）和 16 个优先级。

- 紧耦合的 NVIC 能够达到低延迟的中断响应处理

- 中断向量入口地址直接进入内核

- 紧耦合的 NVIC 接口

- 允许中断的早期处理

- 处理晚到的较高优先级中断

- 支持中断尾部链接功能

- 自动保存处理器状态

- 中断返回时自动恢复，无需额外指令开销

该模块以最小的中断延迟提供灵活的中断管理功能。

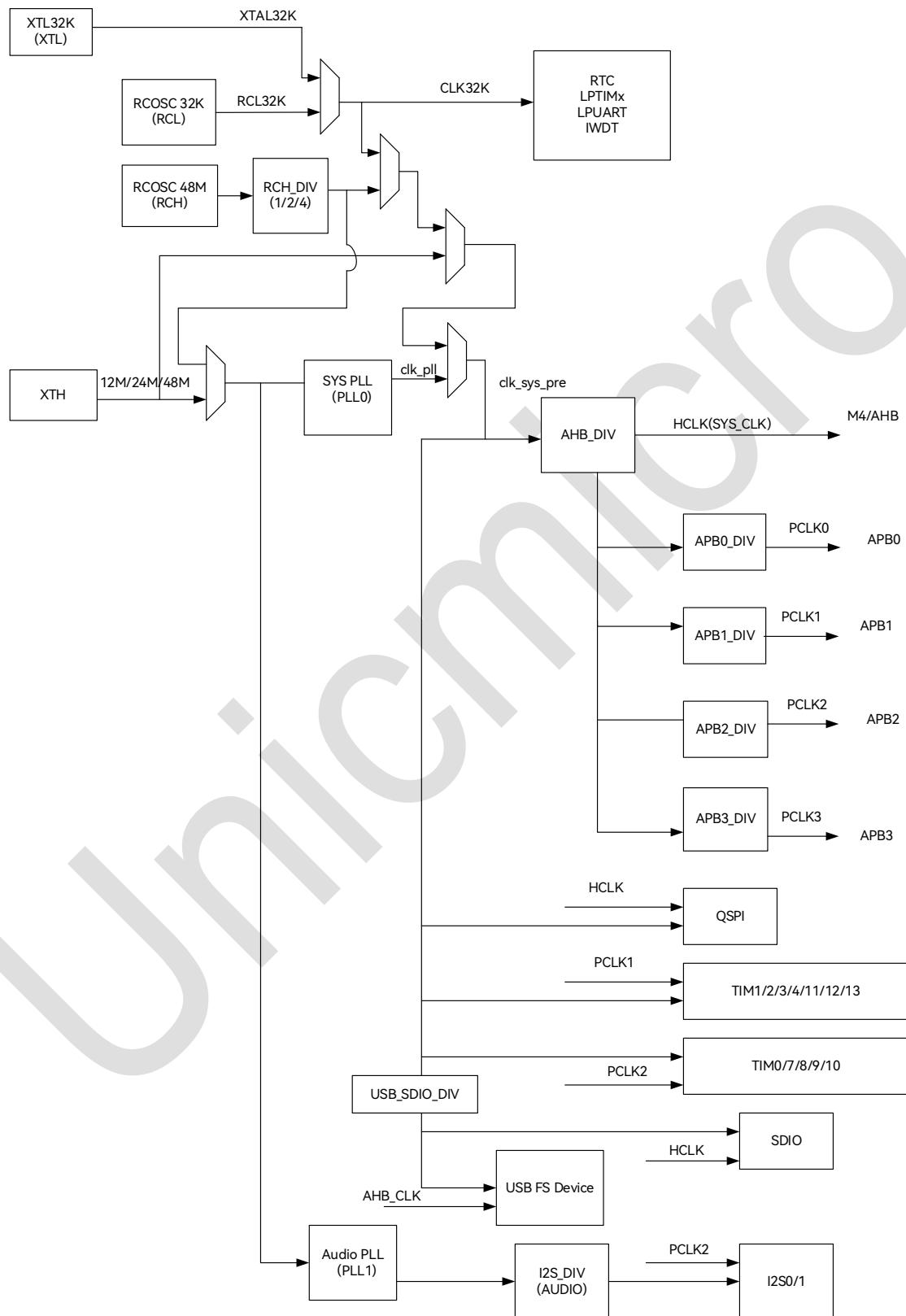

## 2.5 时钟架构 (Clock)

图 2-1: 时钟架构图

系统存在 4 个时钟源：

- 一个频率为 48MHz 的高精度内部时钟 RCH

- 一个频率为 32kHz 的内部时钟 RCL

- 一个频率为 32.768kHz 的外部晶体时钟 XTL

- 支持外部晶体时钟 XTH

内置 2 个 PLL，提供系统时钟、音频时钟和 USB 时钟。

时钟控制单元提供了一系列频率的时钟功能，包括一个内部 48MHz RC 振荡器时钟（RCH）、一个外部高速晶体振荡器时钟（XTH）、一个内部 32kHz RC 振荡器时钟（RCL）、一个外部低速晶体振荡器时钟（XTL）、两个锁相环（PLL）、一个 XTH 时钟监视器、时钟预分频器、时钟多路复用器和时钟门控电路。

AHB、APB、Cortex<sup>TM</sup>-M4 源自系统时钟 (SYS\_CLK)，系统时钟的时钟源可以选择 XTH、RCH、PLL 或低频 32kHz 的 RCL/XTL 时钟。独立看门狗定时器有采用低频的时钟源（RCL 或者 XTL），实时时钟（RTC）使用 RCL 或 XTL 作为时钟源。

## 2.6 复位 (Reset)

芯片复位控制方式如下表所示：

表 2-1：复位方式

| 复位方式              | 产生条件                                    |

|-------------------|-----------------------------------------|

| 上电和掉电复位 (POR&PDR) | $V_{DDH}$ (1.8~3.6V) 上电/掉电和内部 CORE 电压上电 |

| RESETN 引脚复位       | RESETN 外部管脚输入低电平                        |

| 欠压复位 (BOR)        | $V_{DDH}$ 电压降至低于 BOR 电压                 |

| 低电压检测复位 (LVD)     | $V_{DDH}$ 电压降至低于 LVD 电压                 |

| 窗口看门狗复位 (WWDT)    | -                                       |

| 独立看门狗复位 (IWDT)    | -                                       |

| 掉电唤醒复位            | 通过设置掉电模式产生的复位，内核在掉电唤醒事件发生后从复位状态唤醒       |

| 软件复位              | -                                       |

| 外部高速振荡器异常停振复位     | 外部高速振荡器异常停振时产生的复位                       |

## 2.7 电源和电源管理 (PMU)

芯片支持单电源供电和 VBAT 备用电源，外部提供供电电源（1.8~3.6V），内置 LDO 产生内部数字电路工作电压。

VDDH: 1.8~3.6V, VDDH 引脚为 I/O、内部调压器、部分模拟 IP 供电。

VDDA: 1.8~3.6V, VDDA 引脚为 ADC/DAC 等模拟 IP 供电。

VBAT: 1.8~3.6V，在待机模式下可以为 BKSRAM、RTC 等 always-on 模块供电。

支持多种低功耗模式：Sleep 模式、Stop 模式、Standby 模式、DeepStandby 模式。

表 2-2: 低功耗模式表

| Power Modes               | 说明                                                                          | 进入方式                                                                                                                       | 唤醒源                                                                                                                                                                           |

|---------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 工作模式<br>(Run Mode)        | 所有电源上电，高速时钟工作                                                               | -                                                                                                                          | -                                                                                                                                                                             |

| 睡眠模式<br>(Sleep Mode)      | 所有电源上电，M4 核高速时钟关掉，其他保持                                                      | 1. PMU_STANDBY_EN=0,<br>PMU_MODE[1:0]=00,<br>PMU_BKSRAMOFF=0<br>2. EFC_Sys_Mode=0<br>3. WFI 或 WFE                          | 1. 任何 GPIO 中断唤醒<br>2. 任何外设中断唤醒<br>3. 复位唤醒 (RESETN, IWDT 复位)                                                                                                                   |

| 停止模式<br>(Stop Mode)       | 所有电源上电，高速时钟关掉，32K 低速时钟在                                                     | 1. PMU_STANDBY_EN=0,<br>PMU_MODE[1:0]=01,<br>PMU_BKSRAMOFF=0<br>2. EFC_Sys_Mode=0<br>3. M4 核的 SLEEPDEEP =1<br>4. WFI 或 WFE | 1. 任何 GPIO 中断唤醒<br>2. RTC 闹钟中断，RTC 时<br>间戳和侵入中断唤醒<br>3. IWDT 复位或者中断唤<br>醒<br>4. 外部 LPUART 唤醒<br>5. LPTIM0~1 定时唤醒                                                              |

| 待机模式 0<br>(Standby0 Mode) | CORE domain 断电，BBU domain 一直有电，32K 低速时钟运行。<br>BKSRAM/IWDT/LPTIM/LPUART 模块有电 | 1. PMU_STANDBY_EN=1,<br>PMU_MODE[1:0]=10,<br>PMU_BKSRAMOFF=0<br>2. EFC_Sys_Mode=1<br>3. M4 核的 SLEEPDEEP =1<br>4. WFI 或 WFE | 1. 外部管脚 PA0, PA2,<br>PC0, PC2, PC3 唤醒<br>2. RTC 闹钟中断，RTC 时<br>间戳和侵入中断唤醒<br>3. LPTIM0~1 定时唤醒<br>4. LPUART (只有 PC2 管<br>脚唤醒)<br>5. IWDT (复位和中断都<br>支持) 功能唤醒<br>6. 复位唤醒 (RESETN) |

| Power Modes                      | 说明                                                                            | 进入方式                                                                                                                          | 唤醒源                                                                                         |

|----------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| 待机模式 1<br>(Standby1 Mode)        | CORE domain 断电, BBU domain 一直有电, 32K 低速时钟运行。<br>BKSRAM/IWDT/LPTIM/LPUART 模块掉电 | 1. PMU_STANDBY_EN=1,<br>PMU_MODE[1:0]=10,<br>PMU_BKSRAМОFF=1<br>2. EFC_Sys_Mode=1<br>3. 设置 M4 核的 SLEEPDEEP =1<br>4. WFI 或 WFE | 1. 外部管脚 PA0, PA2, PC0, PC2, PC3, PC13 唤醒<br>2. RTC 闹钟中断, RTC 时间戳和侵入中断唤醒<br>3. 复位唤醒 (RESETN) |

| 深度待机模式 0<br>(DeepStandby 0 Mode) | CORE domain 断电, BBU domain 一直有电, 32K 低速时钟不在。<br>BKSRAM/IWDT/LPTIM/LPUART 有电   | 1. PMU_STANDBY_EN=1,<br>PMU_MODE[1:0]=11,<br>PMU_BKSRAМОFF=0<br>2. EFC_Sys_Mode=1<br>3. 设置 M4 核的 SLEEPDEEP =1<br>4. WFI 或 WFE | 1. 外部管脚 PA0, PA2, PC0, PC2, PC3, PC13 唤醒<br>2. 复位唤醒 (RESETN)                                |

| 深度待机模式 1<br>(DeepStandby 1 Mode) | CORE domain 断电, BBU domain 一直有电, 32K 低速时钟不在。<br>BKSRAM/IWDT/LPTIM/LPUART 掉电   | 1. PMU_STANDBY_EN=1,<br>PMU_MODE[1:0]=11,<br>PMU_BKSRAМОFF=1<br>2. EFC_Sys_Mode=1<br>3. 设置 M4 核的 SLEEPDEEP =1<br>4. WFI 或 WFE | 1. 外部管脚 PA0, PA2, PC0, PC2, PC3, PC13 唤醒<br>2. 复位唤醒 (RESETN)                                |

| 掉电模式<br>(Poweroff Mode)          | 所有电源断电                                                                        | 外部 VDDH&VBAT 掉电                                                                                                               | 上电                                                                                          |

注:

- BBU domain 包括 RTC, 备份寄存器和 PMU 逻辑。

- Sleep Mode 和 STOP Mode 支持 IO 保持。

- Standby\* Mode 和 DeepStandby\* Mode, 不支持 IO 保持, 除了外部输入唤醒的 IO, 其他 IO 状态为 High-Impedance 高阻态。唤醒后, IO 管脚状态为上电复位状态。

## 2.8 启动模式

芯片上电后系统从 0x0000\_0000 地址执行。

表 2-3: 启动模式

| BOOT1 (PB2) | BOOT0 | 启动            |

|-------------|-------|---------------|

| 0           | 0     | MAIN FLASH 启动 |

| 1           | 0     | 保留            |

| 0           | 1     | 系统存储器启动       |

| 1           | 1     | SRAM 启动 (保留)  |

注：操作用户区的 BOOT\_SOURCE 地址，可以直接从 MAIN FLASH 启动，加快芯片上电时间。

## 2.9 DMA 控制器 (DMA)

DMA 可以协助 CPU 进行数据搬运的工作，减轻 CPU 的工作负担并提升系统效率。

本芯片内置 2 个 DMA 控制器 (DMA0/DMA1)，总共支持 16 个通道。

主要特性：

- 可以控制多个模块之间的数据传输

- 支持 Memory to Memory 模式、Memory to Peripheral 模式、Peripheral to Memory 模式、Peripheral to Peripheral 模式

- 每个控制器内含有 8 个 DMA 通道

- 数据传输的位宽可设、传输的 Block 长度可设

- 每个通道含有大小为 4x32 的 FIFO

- Block 最大长度可设为 4095

- 支持源地址不变传输、递增传输

- 支持目的地址的不变传输、递增传输

## 2.10 通用异步收发器接口（UART）

通用异步串口收发器（UART）是使用非常广泛的串行通信接口，支持全双工通信。通用异步串口收发器是把存储器或处理器中并行传输的数据串行的发送到外设的 UART 接收端，或接收 UART 外设的串行数据并转换为并行数据提供给处理器。UART 支持与外部接口设备的串行通信。

主要特性：

- 16 字节的硬件 FIFO

- 波特率支持整数和小数分频

- 支持 CTS, RTS 流控制

- 支持错误起始位侦测

- 支持帧中断检测

- 支持断路检测

- 支持数据位宽（5~9 bits），停止位个数（1 bit、1.5 bits 和 2 bits）设置

- 支持对数据进行固定校验、奇偶校验或无校验

- 支持 IrDA 1.0 协议，波特率范围在 9.6k~115.2k

- 支持 DMA 操作

## 2.11 通用同步/异步收发器（USART）

通用同步异步收发器（USART）提供了一个完整的全双工通用同步异步串行链路。为支持最大的标准，数据帧格式可编程范围广（数据长度、奇偶校验、停止位数）。这个接收器实现奇偶校验错误、帧错误和溢出错误检测。接收器超时允许处理可变长度的帧，发送器时间保护便于和慢速远程设备进行通信。多点通信也可通过接收和传输中的地址位处理来支持。

主要特性：

- 可编程波特率发生器

- 5至9位全双工同步或异步串行通信

- 异步模式下 1、1.5 或 2 个停止位，或同步模式下 1 或 2 个停止位模式

- 奇偶校验生成和错误检测

- 帧错误检测、溢出错误检测

- MSB 或 LSB 优先

- 可选的断路符生成和检测

- 8 倍或 16 倍过采样接收机频率

- 可选的硬件握手 RTS - CTS

- 接收器超时和发送器时间保护

- 可选的带有地址生成和检测的多点模式

- IrDA 调制解调

- 通信速率高达 115.2 kbps

- SPI 模式

- 主机或从机

- 串行时钟的相位和极性可编程

- SPI 串行时钟 (SCK) 频率高达内部时钟频率 1/2

- LIN 模式

- 符合 LIN1.3 和 LIN2.0 规范

- 主机或从机

- 处理多达 256 个数据字节的帧

- 响应数据长度可以通过标识符进行配置或自动定义

- 从机节点配置中的自同步

- 自动处理和验证“Synch Break”和“Synch Field”

- 即使“Synch Break”与数据字节部分叠加，也会被检测到

- 自动标识符奇偶校验计算、发送和验证

- 可以禁用奇偶校验发送和验证

- 自动校验和的计算、发送和验证

- 可以禁用校验和的发送和验证

- 支持“经典”和“增强”两种校验和类型

- 完整的 LIN 错误检查和报告

- 支持DMA操作

## 2.12 低功耗串口 (LPUART)

LPUART 是一个低功耗 UART 接口, 工作在 32kHz 时钟下, 最高支持 9600 波特率的数据接收。

主要特性:

- 异步数据收发

- 标准UART帧格式

- 1-bit 起始位

- 7 或 8-bit 数据

- 奇校验、偶校验或无校验位

- 1 或 2-bit 停止位

- 使用32768Hz XTL时钟或者32kHz RCL时钟工作, 支持波特率300 ~ 9600Hz

- 可编程数据极性

- 中断标志

- 接收 Buffer 满标志

- 接收 Buffer 溢出标志

- 接收帧格式错误标志

- 接收校验位错误标志

- START 检测标志

- 数据匹配标志

- 发送完成标志

- 低功耗模式下唤醒芯片

- RXD 下降沿唤醒

- 起始位检测唤醒

- 1 字节接收完成唤醒

- 1 字节数据匹配唤醒

## 2.13 通用输入输出接口 (GPIO)

最多可提供 82 个 GPIO 端口。每个端口由独立的控制寄存器位来控制。支持边沿触发中断和平触发中断，可从各种低功耗模式下把芯片唤醒到工作模式。内置上拉电阻、下拉电阻，带有施密特触发器输入滤波功能。输出驱动能力可配置，最大支持 12mA 的电流驱动能力。82 个通用 IO 可支持外部异步中断。其中 58 个 IO 可以支持 5V 耐压输入。

## 2.14 定时器/计数器 (TIMx)

2 个 32 位高性能计时器 (eQCT<sup>TM</sup>: TIM0/TIM7) , 每个定时器支持 4 路输入捕获, 3 对+1 路 PWM 输出, 3 对死区互补；支持刹车功能；支持系统时钟 2 倍频的 PWM 精度；支持增量正交编码器和霍尔传感器。

10 个 32 位通用定时器 (TIM1/TIM2/TIM3/TIM4/TIM8/TIM9/TIM10/TIM11/TIM12/TIM13) , 每个定时器支持 4 路输入捕获, 4 路 PWM 输出；支持系统时钟 2 倍频的 PWM 精度；支持增量正交编码器和霍尔传感器。

2 个 32 位基本定时器 (TIM5/TIM6) , 可触发 D/A 转换输出。

定时器各功能比较如下：

表 2-4: 定时器功能

| 定时器类型 | 定时器          | 分辨率 | 类型               | 预分频系数           | 产生 DMA 请求 | 捕获/比较通道 | 互补输出 |

|-------|--------------|-----|------------------|-----------------|-----------|---------|------|

| 高级定时器 | TIM0<br>TIM7 | 32  | 向上, 向下,<br>向上/向下 | 1~65536 之间的任意整数 | Y         | 4       | Y    |

| 定时器类型  | 定时器   | 分辨率 | 类型              | 预分频系数           | 产生 DMA 请求 | 捕获/比较通道 | 互补输出 |

|--------|-------|-----|-----------------|-----------------|-----------|---------|------|

| 通用定时器  | TIM1  | 32  | 向上, 向下,向上/向下    | 1~65536 之间的任意整数 | Y         | 4       | N    |

|        | TIM2  |     |                 |                 |           |         |      |

|        | TIM3  |     |                 |                 |           |         |      |

|        | TIM4  |     |                 |                 |           |         |      |

|        | TIM8  |     |                 |                 |           |         |      |

|        | TIM9  |     |                 |                 |           |         |      |

|        | TIM10 |     |                 |                 |           |         |      |

|        | TIM11 |     |                 |                 |           |         |      |

|        | TIM12 |     |                 |                 |           |         |      |

| 基本定时器  | TIM13 |     |                 |                 |           |         |      |

|        | TIM5  | 32  | 向上              | 1~65536 之间的任意整数 | Y         | 0       | N    |

| 低功耗定时器 | TIM6  |     |                 |                 |           |         |      |

| LPTIM0 | 16    | 向上  | 1~65536 之间的任意整数 | N               | 1         | N       | N    |

| LPTIM1 |       |     |                 |                 |           |         |      |

## 2.15 低功耗定时器 (LPTIM)

LPTIM 是运行在 Always-On 电源域下的 16 位低功耗定时器/计数器模块。通过选择合适的工作时钟，LPTIM 在各种低功耗模式下保持运行，并且只消耗很少的电量。LPTIM 可以在没有内部时钟的条件下实现低功耗模式下的外部脉冲计数功能。此外，与外部输入的触发信号结合，可以实现低功耗超时唤醒功能。

主要特性：

- 16 位递增计数器

- 3 位异步时钟分频器，8 种分频系数（1、2、4、8、16、32、64、128）

- 可选工作时钟源：

- 内部时钟源：LSCLK（XTL 或者 RCL）、CLK1HZ、系统 APB0 时钟（PCLK0）

- 外部时钟源：LPTIMx\_IN

- 16 位比较寄存器

- 16 位目标寄存器

- 软件/硬件触发

- 输入极性选择

- 无时钟外部脉冲计数

- 外部触发的低功耗超时唤醒

- 支持 16 位 PWM

## 2.16 I2C 接口 (I2C)

3 路 I2C 接口 (I2C0/I2C1/I2C2) , 支持主从模式。

主要特性:

- 支持主机发送/接收, 从机发送/接收

- 最高支持 1Mbps 工作速率

- 支持 7 位和 10 位寻址功能

- 支持中断状态查询功能

- 接收和发送各 2 个字节深度的 FIFO

- 支持 DMA 加速

## 2.17 实时时钟 (RTC)

实时时钟模块, 支持硬件万年历 (秒、分钟、小时、星期几、日期、月份和年份显示), 同时支持 1 个闹钟、1 个周期性唤醒源、一个篡改检测器和 80 个字节的备份寄存器。

## 2.18 串行音频接口 (I2S)

集成电路内置音频总线 (Inter-IC Sound Bus, I2S) 是由飞利浦 (Philips) 开发的一种标准化的通信接口, 用于许多基于 (超) 大规模集成电路的系统, 尤其是在许多数字立体声音频系统中。

主要特性:

- 支持主机和从机模式

- 支持单工发送、单工接收、双工收发

- 支持飞利浦 (Philips)、左对齐、右对齐、PCM 长/短帧标准

- 声道长度可选 16 位或 32 位

- 音频数据长度可选 8 位、16 位、24 位或 32 位

- 对于非 PCM 标准，支持双声道数据和单声道数据

- 对于双声道音频数据，可选左声道先传输或右声道先传输

- 对于单声道音频数据，可选左声道或右声道传输

- 对于非 PCM 标准，WS 的极性可选

- 对于非 PCM 标准，SD 和 WS 的切换的时刻可选 SCK 的上升或下降沿

对于 PCM 标准，SD 和 WS 的切换的时刻固定为 SCK 的上升沿

- 内置 8 字深的 TXFIFO 和 RXFIFO (1 字 = 32 位)，各自可以储存 16 条 16 位的数据或 8 条 32 位的数据

- 主机模式下需要 PLL 生成的 MCLK，其频率是音频采样率 (Fs) 的 256 倍，音频采样率通常为 8/11.025/16/22.05/24/32/44.1/48/96/192 kHz

- 如果使能了中断，则下列情况会触发中断：

- TXFIFO 有足够空间

- RXFIFO 有足够的数据

- TXFIFO 欠载

- RXFIFO 溢出

- 支持 DMA 操作

## 2.19 控制器局域网络 (CAN)

CAN (Controller Area Network) 控制器可以用于汽车电子和工业控制领域，支持 CAN2.0A/B 协议。

**主要特性:**

- 符合 CAN2.0A, 2.0B 协议

- 支持 CAN 格式

- 支持最大 8 bytes 数据帧

- CAN2.0B 最大数据传输速率 1Mbps

- 64-byte RX FIFO

- 16-byte TX FIFO

- 支持传输停止

- 错误计数器可读

## 2.20 同步串行接口 (SPI)

同步串行接口支持主从模式。支持 DMA 硬件数据传输。

串行外围接口 (SPI) 被广泛用于在 EEPROM、FLASH、微控制器、DAC、ADC 等不同设备之间提供经济的板级接口。

**主要特性:**

- 可配置主机模式或从机模式

- 主机和从机模式下均支持串行的全双工、半双工、单工发送和单工接收操作

- 可配置 16 位 SPI 时钟频率控制寄存器：在主机模式下，SCK 频率最高为 PCLK 频率的 1/2；

在从机模式下，SCK 频率最高为 PCLK 频率的 1/4

- 可配置 SCK 的极性和相位

- 可配置摩托罗拉 (Motorola) 或德州仪器 (TI) 时序模式

- 可配置按最高位或最低位优先的顺序发送和接收数据

- 可配置每个字符长度为 1 至 32 位，默认为 8 位

- 支持数据拼接功能，以充分利用 FIFO 空间

- 具有 8 级 32 位宽的发送 FIFO 和接收 FIFO

- 可配置软件或硬件控制片选

- 支持 DMA 操作

## 2.21 四线 SPI 控制器 (QSPI)

QSPI 控制器可向串行 Flash 器件提供访问权限。支持高性能单线、双线和四线 SPI 标准接口。

主要特性:

- 存储器映射的直接操作模式，用来进行Flash数据传输和执行Flash存储器中的编码

- 软件触发的间接操作模式，用来进行延迟时间短和非处理器密集型的Flash数据传输

- 支持DMA操作

- 软件APB可访问的Flash控制寄存器组可执行任何Flash命令，包括一次数据传输可高达8个字节

- 支持XIP (Execute in Place)，有时也指连续模式

- 支持单线，双线，四线I/O指令

- 器件大小可编程

- 写保护区域可编程，可阻止系统写入生效

- 传输事务之间的延时可编程

- 传统模式下允许软件直接访问底层发送和接收FIFOs，旁路较高层流程

- 支持独立的异步的SPI通信参考时钟

- 串行时钟可配置极性

- 可编程波特率发生器支持生成不同器件时钟

- 包含可提升高速读数据捕捉机制的特性

- 可选择使用调整时钟来进一步提升读数据捕捉

- 可编程中断生成

- 支持1个外部器件

## 2.22 独立看门狗 (IWDT)

看门狗定时器在到达超时的值的时候可以产生不可屏蔽中断或者是复位。当系统由于软件错误或是由于外部设备故障而无法按照预期的方式响应的时候，使用看门狗定时器可以重新获得控制权。

主要特性：

- 32 位递减并且可编程装载的定时器

- 独立的看门狗时钟使能

- 带中断屏蔽的中断生成逻辑

- 软件跑飞保护锁定寄存器

- 软件启动功能：WDT 控制寄存器中复位使能/禁止的设置

- 在调试期间 CPU 暂停时，可暂停定时器计数的寄存器配置

## 2.23 窗口看门狗 (WWDT)

带窗口的看门狗是一个与 CPU 同步运行的看门狗，目的是实时监控 CPU 运行状态，在 CPU 运行异常的情况下复位 CPU，避免不可预计的后果。

为了保证同步性和实时性，WWDT 使用 PCLK 时钟工作，内部有一个预分频电路，以产生同步计数使能信号。

主要特性：

- 计数模式为从 0 开始向上计数到溢出时间

- 窗口开放期为计数器大于或等于溢出时间的 50%

- 支持预警中断功能，在计数到溢出时间的 75%时候中断

## 2.24 硬件加速运算协处理器 (Cordic)

Cordic 控制器可以使用 Cordic 算法计算  $m \cdot \sin \theta$ 、 $m \cdot \cos \theta$ 、 $\text{atan2}(y, x)$ 、 $\sqrt{x^2 + y^2}$ 、 $y \cdot x$ 、 $y/x$ 、 $\sinh w$ 、 $\cosh w$ 、 $\tanh^{-1}(y/x)$ 、 $\ln x$ 、 $\sqrt{x}$  等函数。

主要特性：

- 内部使用 24 位精度计算

- AHB 接口可以输入输出 32 或 16 位数据

## 2.25 安全数字输入输出接口 (SDIO)

SDIO 控制器作为数据传输接口，支持 SD 和 eMMC 标准协议，可作为 SD 卡读卡器和 eMMC 卡读卡器的 master 控制器，也支持安全数字 I/O (SDIO)。

主要特性：

- 支持 SD2.0 和 eMMC4.4.1 协议

- 内置 FIFO，宽度为 32bit，深度为 16，支持当 over-run 和 under-run 时停止时钟

- 支持 CRC 产生和校验

- 支持可编程的波特率。支持一种时钟分配率以满足在不同波特率下通信的要求

- 支持时钟控制开关

- 支持卡检测

- 支持卡写保护

- 支持 1-bit、4-bit、8-bit 模式的 SDIO 中断

- 支持 block size 从 1 到 65536

- 支持 DMA 传输

## 2.26 数字摄像头接口 (DCMI)

DCMI 可以接收来自摄像头的 8/10/12/14 位数据流，支持多种格式和 JPEG 传输。

主要特性：

- 支持 8/10/12/14 位 DVP 接口

- 支持硬件/内嵌码同步

- 支持连续/单帧模式

- 支持窗口剪裁功能

- 支持内置 DMA 传输数据

## 2.27 外部存储接口 (EMC)

模块支持 SRAM, NOR FLASH, I80 接口功能。存储器接口控制器 EMC (External Memory Controller) 负责控制信息的传输，该传输是在内部局部总线和外部存储器模块（同步或者异步）之间进行的。同时此模块也可以作为 TFT-LCD 控制器使用，用来支持 8080 接口的 TFT-LCD。

主要特性：

- 支持片外 SRAM、Norflash 扩展

- 支持 8080 TFT-LCD 控制

- 支持写保护功能

- 支持外部接口 8/16 bit 可配

- 读写操作等待时间可配

## 2.28 以太网接口（EMAC）

EMAC 可以接收和发送以太网数据，符合 IEEE802.3-2002 标准。

主要特性：

- 支持外部 PHY 接口实现 10M/100M/1000M bit/s 的数据传输速率

- 支持 MII 和 RMII、RGMII 接口

- 支持全双工和半双工工作模式

- 使用 MDIO 接口配置和管理 PHY 设备

- 支持以太网时间戳（IEEE 1588-2002），每个帧的发送或接收状态下给出 64 位时间戳

- 报头和帧起始数据（SFD）在发送路径中插入、在接收路径中删除

- 支持帧长有效性检测，丢弃超长帧和超短帧

- 支持对输入帧进行 CRC 校验，可丢弃校验错的帧

- 支持对输出帧添加 CRC 校验

- 支持短帧填充功能

- 支持对接收和发送帧进行统计计数

- 支持广播帧、组播帧和单播帧过滤

- 支持控制报文、IP 报文、广播或多播报文限速处理功能可配置

- 支持包过滤功能

- 支持入队中断和超时中断两种中断方式

- 支持收发包缓存

- 支持 EEE 能效以太网功能

- 相互独立的两个 2K 字节的 FIFO 分别用于发送与接收

## 2.29 随机数（RNG）

RNG 控制器可以产生随机数。可以利用随机数种子产生随机数。

## 2.30 高级加解密算法加速器 (AES)

AES 模块可以实现 FIPS PUB 197 中定义的 AES-128 或 AES-256 算法。

主要特性:

- 支持 128 位和 256 位密钥长度

- 支持 CBC、ECB、ETR、CCM、CMAC 和 GCM 模式

- 支持加密和解密

- 按照 AES 规格规定，所有数据为大端对齐

- 密钥和信息使用分离的储存接口，密钥使用低容量储存，输入输出数据使用 FIFO 与接口交互

- 数据输入输出采用 DMA 进行操作

- 可用即时密钥拓展，无需额外储存空间

- 对于一个信息，仅支持基于分组的加解密，不支持信息切换

- 支持 3 密钥模式

## 2.31 安全散列算法加速器 (SHA)

SHA 模块可以实现 FIPS PUB 180-4 中定义的 SHA-256 算法。

主要特性:

- 支持 256 位 ICV 长度

- 需要外部储存中的信息使用小端对齐且对齐到双字

- 使用 32 x 32 bits 的输入数据 FIFO

- 数据输入可采用 DMA 进行操作

## 2.32 USB FS Device 接口 (USB)

USB 设备控制器是一个兼容 USB2.0 全速协议设备接口，其与 USB PHY 配合使用，提供芯片与 USB HOST 通讯功能。

主要特性：

- 兼容 USB1.1 和 USB2.0 全速协议

- 含有 4 个通用双向传输 End Point (EP1、EP2、EP3、EP4)

- End Point 支持最大包长度 64 bytes，支持 Memory 和 FIFO 两种访问功能

- FIFO 模式支持 32-bit 方式访问

- Memory 访问支持 8、16、32-bit 三种访问方式

- 支持挂起、唤醒和远程唤醒功能

- 支持 Toggle 硬件比对与软件控制功能

- 支持每一个 End Point 数据传输产生中断功能

- 支持 Bus Reset、Suspend 和 Resume 中断功能

- 支持可选的 CRC 错误回复 NAK 功能

- 支持数据包超过最大包长度 (64 bytes) 自动回复 NAK 功能

- 支持 IN 操作主机未回 ACK，接下来 IN 操作 USB 设备回复 NAK 功能

- 支持令牌包与数据包 EOP 丢失检测，支持可选的丢失 EOP 自动回复 NAK 功能

## 2.33 模拟/数字转换器 (ADC)

支持 2 个 12 位 5.25Msps 采样率的 SAR ADC，支持单端输入和差分输入，可测量 16 个外部通道，1 个内部通道。

主要特性：

- 分辨率 12 位的逐次型 ADC

- ADC 供电要求：1.8~3.6V；ADC 输入范围： $V_{REF-} \leq V_{IN} \leq V_{REF+}$

- $V_{REF}$  参考源可选:  $V_{DDA}$ , 内部 1.5/2.0/2.5/3V  $V_{REF}$ , 或者外部输入  $V_{REFP}$

- 2 个 ADC 可与内部运算放大器 (OPA) 配合使用, 在采样之前先放大信号或者作为 BUFFER

- 触发方式可由软件配置寄存器触发, 或内部定时器事件 (上升沿、下降沿或双边沿) 触发, 或 GPIOA 中断触发

- 转换模式有单次模式、连续模式、断续模式、双 ADC 协同模式

- 有常规序列和注入序列。常规序列最多包含 16 个通道转换的位置, 注入序列最多包含 4 个通道转换的位置, 常规序列和注入序列中的每个位置可以选择任意一个通道。注入序列的优先级高于常规序列。

- 可连续多次 (2, 4, 8, 16, 32, 64 或 128 次) 对某个或某些通道采样转换并计算平均数

- 支持模拟看门狗功能, 监视转换结果

- 每个通道都有独立的数据寄存器, 可统一设定读取后是否自动清除数据

- 两个 ADC 控制器各有一个 32 级深、16 位宽的接收器 FIFO, 用于保存常规序列和注入序列的转换结果

- 支持 DMA 模式

## 2.34 数字/模拟转换器 (DAC)

内置 2 个独立的 D/A 转换模块, 可以控制数模转换器将 12 位数字量转换为模拟电压输出。

主要特性:

- 支持 8/12 位数字输入

- 支持两个转换器同时更新转换数据

- 支持产生三角波和噪声波

- 支持 DMA 操作

- 支持外部触发更新转换数据

## 2.35 运算放大器 (OPA)

主要特性:

- 支持 OPA 功能

- 支持 1/2/4/8x 的单端 PGA 功能（采用内部反馈电阻），以及支持 1/2/4/8/16/32/64x 的 PGA 功能（采用外部反馈电阻）

- 可作为模拟比较器使用

- 可作为 BUFFER，与 ADC 配合使用

## 2.36 模拟比较器 (ACMP)

ACMP 模块用于比较两个输入模拟电压的大小，并根据比较结果输出高/低电平。当“INP”输入端电压高于“INM”输入端电压时，比较器输出为高电平，当“INP”输入端电压低于“INM”输入端电压时，比较器输出为低电平。

主要特性:

- 模拟比较器输出，可以产生中断。

## 2.37 温度传感器 (TS)

温度传感器产生一个随温度线性变化的电压，内置独立的 A/D 转换电路，用于将温度传感器的输出转换到数字数值。

## 2.38 安全系统

### 2.38.1 唯一 ID 号

每颗芯片出厂前具备唯一的 16-byte 设备标识号，包括 wafer lot 信息，以及芯片坐标信息等。

## 2.38.2 CRC16/32 硬件循环冗余校验码

CRC 控制器可以以多种多项式进行循环冗余计算。

主要特性:

- 支持以下多项式:

- $x^{16} + x^{12} + x^5 + 1$

- $x^{16} + x^{15} + x^2 + 1$

- $x^{32} + x^{26} + x^{23} + x^{22} + x^{16} + x^{12} + x^{11} + x^{10} + x^8 + x^7 + x^5 + x^4 + x^2 + x^1 + 1$

- 支持输入字节、半字、字型数据

- 支持输入数据按字、半字、字节倒序、初始值倒序、结果值倒序

## 2.39 调试和编程系统

调试和编程系统特性如下:

- **嵌入式调试系统**

嵌入式调试解决方案，提供全功能的实时调试器，配合标准成熟的 Keil/IAR 等调试开发软件，支持 4 个硬断点以及多个软断点。

- **在线编程模式**

支持在线编程，复位完成后的数毫秒为 ISP 模式，之后进入用户模式。

- **高安全性**

加密型嵌入式调试解决方案，提供全功能的实时调试器。

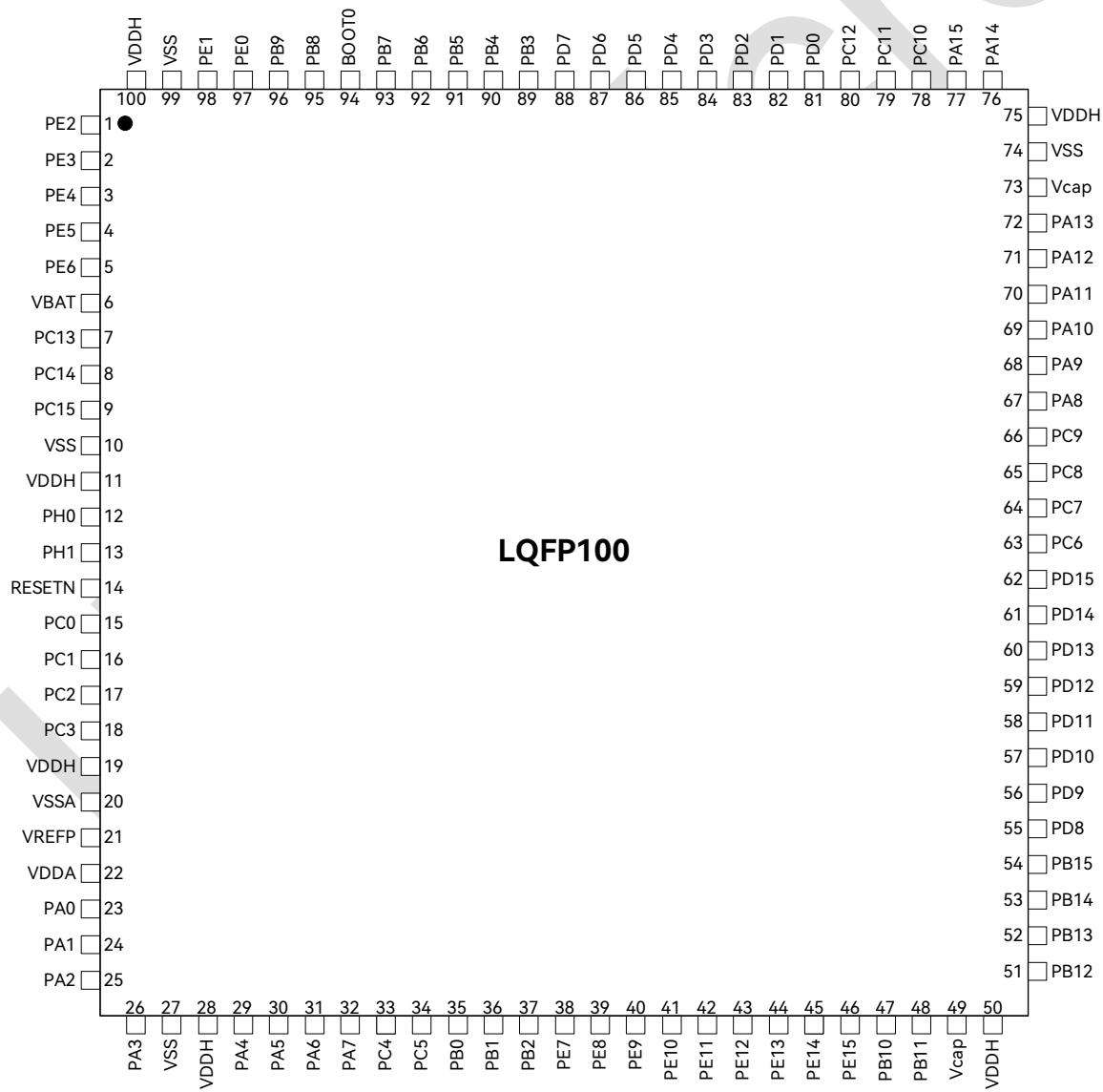

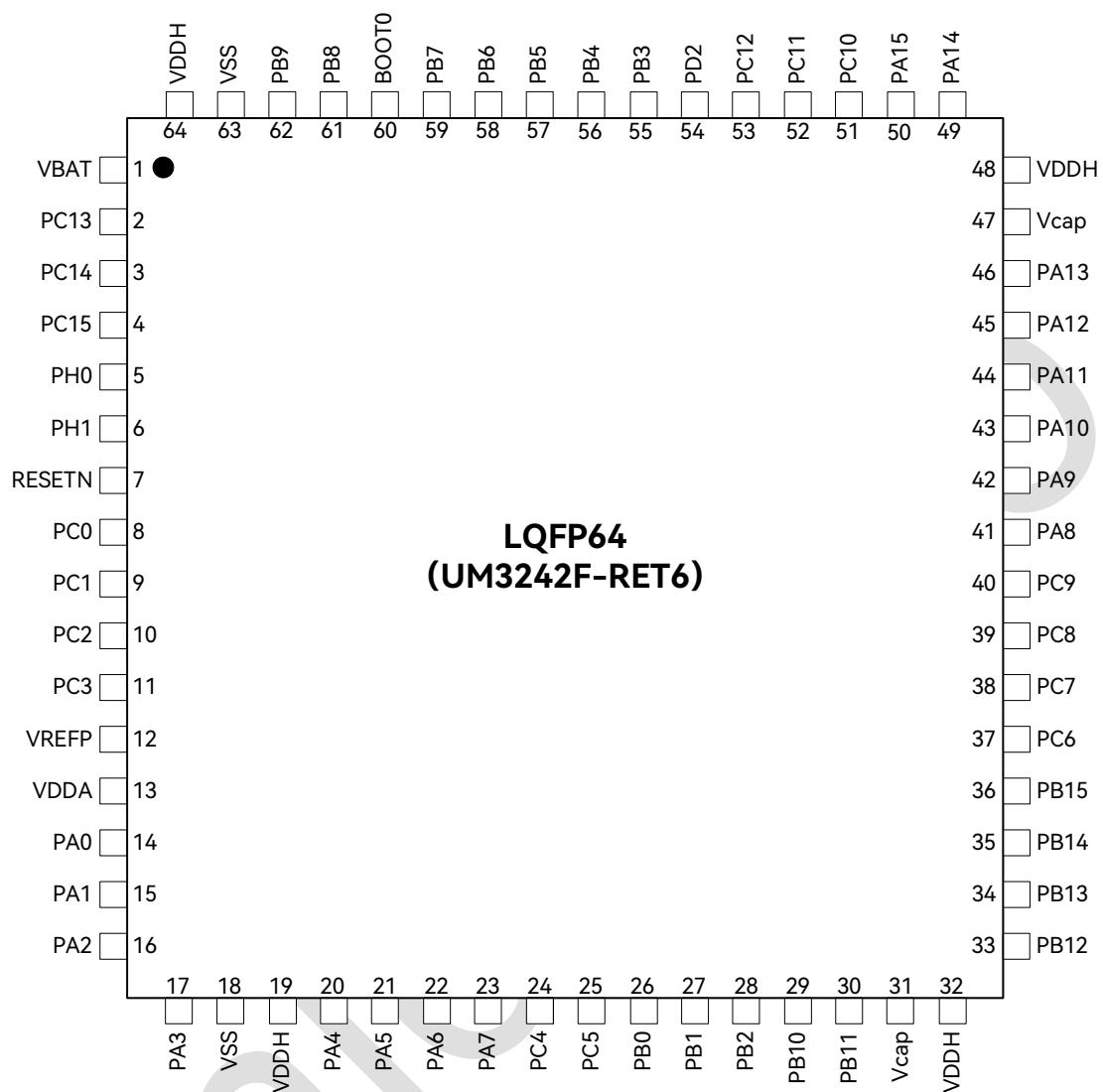

# 3 引脚定义和描述

## 3.1 引脚定义

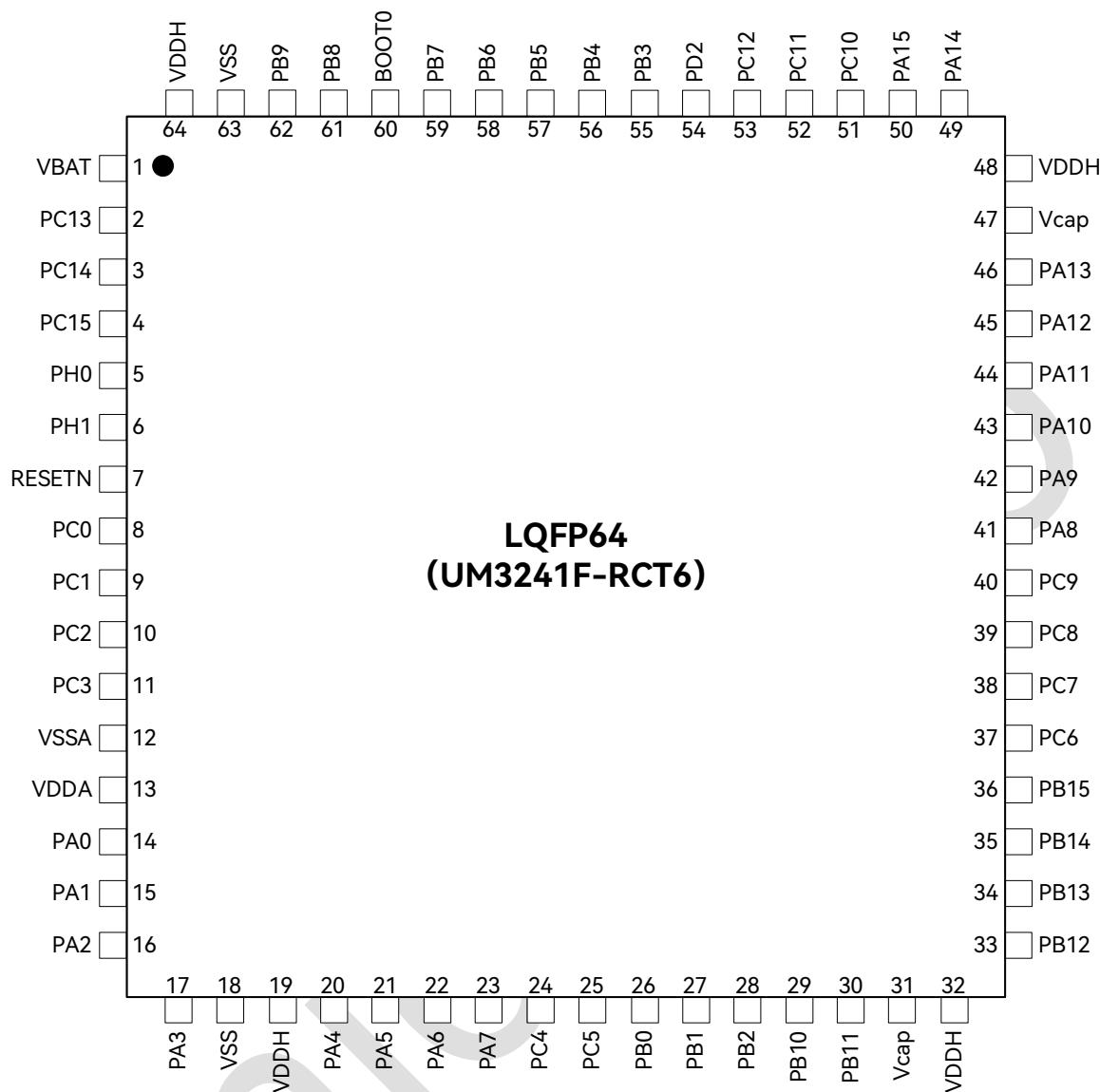

芯片有多种封装。管脚功能由 IO 控制寄存器配置，除电源管脚和 RESETN 复位管脚外，其余管脚均可复用。系统复位后，管脚功能将被设置成默认值。

注：最终封装可能会有个别管脚存在差异。

图 3-1：LQFP100 引脚分布图

图 3-2: LQFP64 引脚分布图 (UM3242F-RET6)

图 3-3: LQFP64 引脚分布图 (UM3241F-RCT6)

## 3.2 引脚描述

表 3-1: 缩写词定义

| 名称   | 缩写  | 定义                                            |

|------|-----|-----------------------------------------------|

| 引脚名称 |     | 除非在引脚名称下使用括号特别说明，否则在复位期间和复位之后的引脚功能均与实际引脚名称相同。 |

| 类型   | S   | 电源引脚                                          |

|      | I   | 仅输入引脚                                         |

|      | I/O | 输入/输出引脚                                       |

| 名称     | 缩写                                                     | 定义                                     |

|--------|--------------------------------------------------------|----------------------------------------|

| I/O 结构 | FT                                                     | 5V 耐压 I/O, 支持 Fail-Safe                |

|        | TTa                                                    | 支持 fail-safe, 3.3V 耐压 I/O, 直接连接到 ADC 等 |

|        | B                                                      | 专用 BOOT0 引脚                            |

|        | RST                                                    | 嵌入了弱上拉电阻的输入复位引脚                        |

| 复用功能   | 通过 GPIOx_AFR 寄存器选择的功能                                  |                                        |

| 可选功能   | 通过外设寄存器直接选择/使能                                         |                                        |

| 说明     | 除非通过注释特别说明, 否则所有 I/O 在复位期间和复位之后均设置为悬空输入<br>(模拟功能, 高阻态) |                                        |

表 3-2: 引脚定义

| 引脚编号 | LQFP100 | LQFP64 <sup>+</sup> | 引脚名称<br>(复位后) | 类型  | I/O<br>结构 | Fail<br>safe<br>支持 | 可选的复用功能                                                                  |      | 说明 |

|------|---------|---------------------|---------------|-----|-----------|--------------------|--------------------------------------------------------------------------|------|----|

|      |         |                     |               |     |           |                    | 复用功能                                                                     | 可选功能 |    |

| 1    | -       |                     | PE2           | I/O | FT        | Yes                | TRACECK/<br>ETH_TXD3/<br>EMC_A10                                         | -    | -  |

| 2    | -       |                     | PE3           | I/O | FT        | Yes                | TRACED0/<br>TIM8_CH3/<br>SPI3_SCK/<br>EMC_A11                            | -    | -  |

| 3    | -       |                     | PE4           | I/O | FT        | Yes                | TRACED1/<br>LPTIM1_OUT/<br>TIM8_CH4/<br>SPI3_NSS/<br>EMC_A12/<br>DCMI_D4 | -    | -  |

| 4    | -       |                     | PE5           | I/O | FT        | Yes                | TRACED2/<br>TIM8_CH1/<br>SPI3_MISO/<br>EMC_A13/<br>DCMI_D6               | -    | -  |

| 5    | -       |                     | PE6           | I/O | FT        | Yes                | TRACED3/<br>TIM8_CH2/<br>SPI3_MOSI/<br>EMC_A14/<br>DCMI_D7               | -    | -  |

| 引脚编号<br>LQFP100<br>LQFP64              |                         | 引脚名称<br>(复位后)   | 类型  | I/O<br>结构 | Fail<br>safe<br>支持 | 可选的复用功能                                                                                   |                        | 说明                                             |

|----------------------------------------|-------------------------|-----------------|-----|-----------|--------------------|-------------------------------------------------------------------------------------------|------------------------|------------------------------------------------|

|                                        |                         |                 |     |           |                    | 复用功能                                                                                      | 可选功能                   |                                                |

| 6                                      | 1                       | VBAT            | S   | -         | -                  | -                                                                                         | -                      | 不使用此管脚时，外加电容接地                                 |

| 7                                      | 2                       | PC13-TAMPER-RTC | I/O | TTa       | Yes                | -                                                                                         | TAMPER-RTC/<br>WKUP    | 只支持 tamper 功能，还有 GPIO 功能。<br>RESETN=0，此管脚有内部下拉 |

| 8                                      | 3                       | PC14-XTL_IN     | I/O | TTa       | Yes                | -                                                                                         | XTL_IN                 | -                                              |

| 9                                      | 4                       | PC15-XTL_OUT    | I/O | TTa       | Yes                | -                                                                                         | XTL_OUT                | -                                              |

| 10/<br>27/<br>74/<br>99                | 18/<br>63               | VSS             | S   | -         | -                  | -                                                                                         | -                      | -                                              |

| 11/<br>19/<br>28/<br>50/<br>75/<br>100 | 19/<br>32/<br>48/<br>64 | VDDH            | S   | -         | -                  | -                                                                                         | -                      | -                                              |

| 12                                     | 5                       | PH0-XTH_IN      | I/O | TTa       | -                  | -                                                                                         | XTH_IN                 | -                                              |

| 13                                     | 6                       | PH1-XTH_OUT     | I/O | TTa       | -                  | -                                                                                         | XTH_OUT                | -                                              |

| 14                                     | 7                       | RESETN          | I   | RST       | -                  | -                                                                                         | -                      | 默认上拉                                           |

| 15                                     | 8                       | PC0             | I/O | TTa       | Yes                | LPTIM0_IN/<br>TIM4_CH1/<br>USART6_CTS/<br>EMC_A4                                          | ADC_IN10/<br>ACMP2_INM | -                                              |

| 16                                     | 9                       | PC1             | I/O | TTa       | Yes                | LPTIM0_OUT/<br>TIM4_CH2/<br>USART6 RTS/<br>ETH_MDC/<br>EMC_A5/<br>EVENTOUT                | ADC_IN11/<br>ACMP2_INP | -                                              |

| 17                                     | 10                      | PC2             | I/O | TTa       | Yes                | LPUART_RX/<br>TIM4_CH3/<br>SPI1_MISO/<br>I2S0_EXTSD/<br>USART6_TX/<br>ETH_TXD2/<br>EMC_A6 | ADC_IN12               | -                                              |

| 引脚编号<br>LQFP100<br>LQFP64 <sup>+</sup> |    | 引脚名称<br>(复位后)                                    | 类型  | I/O<br>结构 | Fail<br>safe<br>支持 | 可选的复用功能                                                                                                     |                       | 说明              |

|----------------------------------------|----|--------------------------------------------------|-----|-----------|--------------------|-------------------------------------------------------------------------------------------------------------|-----------------------|-----------------|

|                                        |    |                                                  |     |           |                    | 复用功能                                                                                                        | 可选功能                  |                 |

| 18                                     | 11 | PC3                                              | I/O | TTa       | Yes                | LPTIM0_TRIG/<br>TIM4_CH4/<br>SPI1_MOSI/<br>I2S0_SD/<br>USART6_RX/<br>ETH_TX_CLK/<br>EMC_A7                  | ADC_IN13              | -               |

| 20                                     | -  | VSSA/<br>VERFN (VREF-)                           | S   | -         | -                  | -                                                                                                           | -                     | VREF-与 VREFN 相同 |

| 21                                     | 12 | VREFP (VREF+)                                    | S   | -         | -                  | -                                                                                                           | -                     | VREF+与 VREFP 相同 |

|                                        | 12 | VSSA/<br>VERFN (VREF-)<br>(仅适用于<br>UM3241F-RCT6) | S   | -         | -                  | -                                                                                                           | -                     | VREF-与 VREFN 相同 |

| 22                                     | 13 | VDDA                                             | S   | -         | -                  | -                                                                                                           | -                     | -               |

| 23                                     | 14 | PA0                                              | I/O | TTa       | Yes                | TIM1_CH1_ETR/<br>TIM4_CH1/<br>TIM7_ETR/<br>UART1_CTS/<br>UART3_TX/<br>USART6_CTS/<br>ETH_CRS                | ADC_IN0/<br>OPA0_VINP | -               |

| 24                                     | 15 | PA1                                              | I/O | TTa       | Yes                | TIM1_CH2/<br>TIM4_CH2/<br>UART1_RTS/<br>UART3_RX/<br>USART6_RTS/<br>ETH_RX_CLK/<br>ETH_REF_50M/<br>EVENTOUT | ADC_IN1/<br>OPA0_VINM | -               |

| 25                                     | 16 | PA2                                              | I/O | TTa       | Yes                | TIM1_CH3/<br>TIM4_CH3/<br>TIM8_CH1/<br>UART1_TX/<br>UART3_CTS/<br>USART6_TX/<br>QSPI_CSN/<br>ETH_MDIO       | ADC_IN2               | -               |

| 引脚编号<br>LQFP100<br>LQFP64 <sup>+</sup> |    | 引脚名称<br>(复位后) | 类型  | I/O<br>结构 | Fail<br>safe<br>支持 | 可选的复用功能                                                                                     |                        | 说明                          |

|----------------------------------------|----|---------------|-----|-----------|--------------------|---------------------------------------------------------------------------------------------|------------------------|-----------------------------|

|                                        |    |               |     |           |                    | 复用功能                                                                                        | 可选功能                   |                             |

| 26                                     | 17 | PA3           | I/O | TTa       | Yes                | TIM1_CH4/<br>TIM4_CH4/<br>TIM8_CH2/<br>UART1_RX/<br>UART3 RTS/<br>USART6_RX/<br>ETH_COL     | ADC_IN3/<br>OPA0_VOUT  | -                           |

| 29                                     | 20 | PA4           | I/O | TTa       | No                 | LPUART_TX/<br>TIM0_CH3/<br>SPI0 NSS/<br>SPI2 NSS/<br>I2S1 WS/<br>USART6 CK/<br>DCMI_HSYNC   | DAC0_OUT               | 备注 2; 不能作为外部<br>ADC 输入通道使用。 |

| 30                                     | 21 | PA5           | I/O | TTa       | Yes                | TIM1_CH1_ETR/<br>TIM0_CH4/<br>TIM7_CH1N/<br>SPI0_SCK/<br>TIM12_CH2                          | DAC1_OUT               | 备注 2; 不能作为外部<br>ADC 输入通道使用。 |

| 31                                     | 22 | PA6           | I/O | TTa       | Yes                | TIM0_BKIN/<br>TIM2_CH1/<br>TIM7_BKIN/<br>SPI0_MISO/<br>TIM12_CH1/<br>DCMI_PIXCLK            | ADC_IN6/<br>OPA1_VINP  | -                           |

| 32                                     | 23 | PA7           | I/O | TTa       | Yes                | TIM0_CH1N/<br>TIM2_CH2/<br>TIM7_CH1N/<br>SPI0_MOSI/<br>TIM13_CH1/<br>ETH_RX_DV/<br>EVENTOUT | ADC_IN7/<br>OPA1_VINM  | -                           |

| 33                                     | 24 | PC4           | I/O | TTa       | Yes                | CLK1HZ/<br>TIM9_CH1/<br>USART6 CK/<br>ETH_RXD0/<br>EMC_A8                                   | ADC_IN14/<br>ACMP1_INM | -                           |

| 引脚编号<br>LQFP100<br>LQFP64 <sup>+</sup> |    | 引脚名称<br>(复位后) | 类型  | I/O<br>结构 | Fail<br>safe<br>支持 | 可选的复用功能                                                                      |                        | 说明                 |

|----------------------------------------|----|---------------|-----|-----------|--------------------|------------------------------------------------------------------------------|------------------------|--------------------|

|                                        |    |               |     |           |                    | 复用功能                                                                         | 可选功能                   |                    |

| 34                                     | 25 | PC5           | I/O | TTa       | Yes                | RTC_VLD_ON/<br>TIM9_CH2/<br>USART7_CTS/<br>ETH_RXD1/<br>EMC_A9               | ADC_IN15/<br>ACMP1_INP | -                  |

| 35                                     | 26 | PB0           | I/O | TTa       | Yes                | TIM0_CH2N/<br>TIM2_CH3/<br>TIM7_CH2N/<br>TIM12_CH3/<br>ETH_RXD2              | ADC_IN8/<br>OPA1_VOUT  | -                  |

| 36                                     | 27 | PB1           | I/O | TTa       | Yes                | TIM0_CH3N/<br>TIM2_CH4/<br>TIM7_CH3N/<br>TIM12_CH4/<br>ETH_RXD3/<br>EVENTOUT | ADC_IN9/<br>ACMP0_INM  | -                  |

| 37                                     | 28 | PB2           | I/O | TTa       | Yes                | TIM9_CH3/<br>TIM12_CH1                                                       | ACMP0_INP              | BOOT1 输入， 默认输入下拉电阻 |

| 38                                     | -  | PE7           | I/O | FT        | Yes                | TIM0_ETR/<br>TIM13_CH2/<br>EMC_D4/<br>EVENTOUT                               | -                      | -                  |

| 39                                     | -  | PE8           | I/O | FT        | Yes                | TIM0_CH1N/<br>TIM13_CH3/<br>EMC_D5                                           | -                      | -                  |

| 40                                     | -  | PE9           | I/O | FT        | Yes                | TIM0_CH1/<br>EMC_D6                                                          | -                      | -                  |

| 41                                     | -  | PE10          | I/O | FT        | Yes                | TIM0_CH2N/<br>TIM13_CH4/<br>QSPI_SCK/<br>EMC_D7                              | -                      | -                  |

| 42                                     | -  | PE11          | I/O | FT        | Yes                | TIM0_CH2/<br>EMC_D8/<br>QSPI_CSN                                             | -                      | -                  |

| 43                                     | -  | PE12          | I/O | FT        | Yes                | TIM0_CH3N/<br>TIM13_CH1/<br>QSPI_DIO0/<br>EMC_D9/<br>EVENTOUT                | -                      | -                  |

| 引脚编号<br>LQFP100<br>LQFP64 <sup>+</sup> |           | 引脚名称<br>(复位后)    | 类型  | I/O<br>结构 | Fail<br>safe<br>支持 | 可选的复用功能                                                                                                                      |      | 说明 |

|----------------------------------------|-----------|------------------|-----|-----------|--------------------|------------------------------------------------------------------------------------------------------------------------------|------|----|

|                                        |           |                  |     |           |                    | 复用功能                                                                                                                         | 可选功能 |    |

| 44                                     | -         | PE13             | I/O | FT        | -                  | TIM0_CH3/<br>QSPI_DIO1/<br>EMC_D10                                                                                           | -    | -  |

| 45                                     | -         | PE14             | I/O | FT        | -                  | TIM0_CH4/<br>QSPI_DIO2/<br>EMC_D11                                                                                           | -    | -  |

| 46                                     | -         | PE15             | I/O | FT        | Yes                | TIM0_BKIN/<br>QSPI_DIO3/<br>EMC_D12                                                                                          | -    | -  |

| 47                                     | 29        | PB10             | I/O | FT        | Yes                | TIM1_CH3/<br>LPUART_RX/<br>I2C1_SCL/<br>SPI1_SCK/<br>I2S0_CK/<br>UART2_TX/<br>QSPI_SCK/<br>ETH_RX_ER/<br>EMC_A0              | -    | -  |

| 48                                     | 30        | PB11             | I/O | FT        | Yes                | TIM1_CH4/<br>LPUART_TX/<br>I2C1_SDA/<br>UART2_RX/<br>ETH_TX_EN/<br>EMC_A1                                                    | -    | -  |

| 49/<br>73                              | 31/<br>47 | V <sub>cap</sub> | S   | -         | -                  | -                                                                                                                            | -    | -  |

| 51                                     | 33        | PB12             | I/O | FT        | Yes                | TIM0_BKIN/<br>I2C1_SDA/<br>SPI1_NSS/<br>I2S0_WS/<br>UART5_CTS/<br>CAN1_RX/<br>TIM11_CH3/<br>ETH_TXD0/<br>EMC_A2/<br>EVENTOUT | -    | -  |

| 引脚编号<br>LQFP100<br>LQFP64 <sup>+</sup> |    | 引脚名称<br>(复位后) | 类型  | I/O<br>结构 | Fail<br>safe<br>支持 | 可选的复用功能                                                                                                          |      | 说明 |

|----------------------------------------|----|---------------|-----|-----------|--------------------|------------------------------------------------------------------------------------------------------------------|------|----|

|                                        |    |               |     |           |                    | 复用功能                                                                                                             | 可选功能 |    |

| 52                                     | 34 | PB13          | I/O | FT        | Yes                | TIM0_CH1N/<br>SPI1_SCK/<br>I2S0_CK/<br>UART2_CTS/<br>UART5_RTS/<br>CAN1_TX/<br>TIM11_CH4/<br>ETH_RXD1/<br>EMC_A3 | -    | -  |

| 53                                     | 35 | PB14          | I/O | FT        | Yes                | TIM0_CH2N/<br>TIM7_CH2N/<br>I2C1_SCL/<br>SPI1_MISO/<br>I2S0_EXTSD/<br>UART2_RTS/<br>TIM11_CH1                    | -    | -  |

| 54                                     | 36 | PB15          | I/O | FT        | Yes                | TIM0_CH3N/<br>TIM7_CH3N/<br>I2C1_SDA/<br>SPI1_MOSI/<br>I2S0_SD/<br>TIM11_CH2                                     | -    | -  |

| 55                                     | -  | PD8           | I/O | FT        | Yes                | UART2_TX/<br>TIM12_CH2/<br>EMC_D13                                                                               | -    | -  |

| 56                                     | -  | PD9           | I/O | FT        | Yes                | UART2_RX/<br>TIM12_CH3/<br>EMC_D14                                                                               | -    | -  |

| 57                                     | -  | PD10          | I/O | FT        | Yes                | LPTIM1_IN/<br>TIM12_CH4/<br>EMC_D15                                                                              | -    | -  |

| 58                                     | -  | PD11          | I/O | FT        | Yes                | LPTM1_TRIG/<br>UART2_CTS/<br>EMC_A16                                                                             | -    | -  |

| 59                                     | -  | PD12          | I/O | FT        | Yes                | TIM3_CH1/<br>UART2_RTS/<br>EMC_A17/<br>EVENTOUT                                                                  | -    | -  |

| 引脚编号<br>LQFP100<br>LQFP64 <sup>+</sup> |    | 引脚名称<br>(复位后) | 类型  | I/O<br>结构 | Fail<br>safe<br>支持 | 可选的复用功能                                                                                             |      | 说明 |

|----------------------------------------|----|---------------|-----|-----------|--------------------|-----------------------------------------------------------------------------------------------------|------|----|

|                                        |    |               |     |           |                    | 复用功能                                                                                                | 可选功能 |    |

| 60                                     | -  | PD13          | I/O | FT        | Yes                | TIM3_CH2/<br>EMC_A18                                                                                | -    | -  |

| 61                                     | -  | PD14          | I/O | FT        | Yes                | TIM3_CH3/<br>EMC_D0                                                                                 | -    | -  |

| 62                                     | -  | PD15          | I/O | FT        | Yes                | TIM3_CH4/<br>EMC_D1                                                                                 | -    | -  |

| 63                                     | 37 | PC6           | I/O | FT        | Yes                | TIM2_CH1/<br>TIM7_CH1/<br>I2S0_MCLK/<br>UART5_TX/<br>USART7_TX/<br>SDIO_D6/<br>DCMI_D0              | -    | -  |

| 64                                     | 38 | PC7           | I/O | FT        | Yes                | TIM2_CH2/<br>TIM7_CH2/<br>I2S1_MCLK/<br>UART5_RX/<br>USART7_RX/<br>SDIO_D7/<br>DCMI_D1/<br>EVENTOUT | -    | -  |

| 65                                     | 39 | PC8           | I/O | FT        | Yes                | TIM2_CH3/<br>TIM7_CH3/<br>USART7_CK/<br>SDIO_D0/<br>DCMI_D2                                         | -    | -  |

| 66                                     | 40 | PC9           | I/O | FT        | Yes                | MCO1/<br>TIM2_CH4/<br>TIM7_CH4/<br>I2C2_SDA/<br>USART7_RTS/<br>SDIO_D1/<br>DCMI_D3                  | -    | -  |

| 67                                     | 41 | PA8           | I/O | FT        | Yes                | MCO0/<br>TIM0_CH1/<br>I2C2_SCL                                                                      | -    | -  |

| 引脚编号<br>LQFP100<br>LQFP64 <sup>+</sup> |    | 引脚名称<br>(复位后) | 类型  | I/O<br>结构 | Fail<br>safe<br>支持 | 可选的复用功能                                                                                 |        | 说明               |

|----------------------------------------|----|---------------|-----|-----------|--------------------|-----------------------------------------------------------------------------------------|--------|------------------|

|                                        |    |               |     |           |                    | 复用功能                                                                                    | 可选功能   |                  |

| 68                                     | 42 | PA9           | I/O | FT        | Yes                | TIM0_CH2/<br>I2C2_SDA/<br>UART0_TX/<br>DCMI_D0                                          | -      | -                |

| 69                                     | 43 | PA10          | I/O | FT        | Yes                | TIM0_CH3/<br>UART0_RX/<br>DCMI_D1                                                       | -      | -                |

| 70                                     | 44 | PA11          | I/O | TTa       | -                  | TIM0_CH4/<br>UART0_CTS/<br>CAN0_RX                                                      | USB_DM | -                |

| 71                                     | 45 | PA12          | I/O | TTa       | -                  | TIM0_ETR/<br>UART0_RTS/<br>CAN0_TX/<br>EVENTOUT                                         | USB_DP | -                |

| 72                                     | 46 | PA13          | I/O | FT        | Yes                | SWDIO-JTMS                                                                              | -      | 默认 SWDIO, 内部上拉电阻 |

| 76                                     | 49 | PA14          | I/O | FT        | Yes                | SWCLK-JTCK                                                                              | -      | 默认 SWCLK, 内部上拉电阻 |

| 77                                     | 50 | PA15          | I/O | FT        | Yes                | JTDI/<br>TIM1_CH1_ETR/<br>TIM9_CH2/<br>SPI0_NSS/<br>SPI2_NSS/<br>I2S1_WS                | -      | 默认 JTDI, 内部上拉电阻  |

| 78                                     | 51 | PC10          | I/O | FT        | Yes                | TIM9_CH4/<br>I2S1_CK/<br>SPI2_SCK/<br>UART2_TX/<br>UART3_TX/<br>SDIO_D2/<br>DCMI_D8     | -      | -                |

| 79                                     | 52 | PC11          | I/O | FT        | Yes                | TIM9_CH3/<br>I2S1_EXTSD/<br>SPI2_MISO/<br>UART2_RX/<br>UART3_RX/<br>SDIO_D3/<br>DCMI_D4 | -      | -                |

| 引脚编号 |    | 引脚名称<br>(复位后) | 类型  | I/O<br>结构 | Fail<br>safe<br>支持 | 可选的复用功能                                                                                      |      | 说明 |

|------|----|---------------|-----|-----------|--------------------|----------------------------------------------------------------------------------------------|------|----|

|      |    |               |     |           |                    | 复用功能                                                                                         | 可选功能 |    |

| 80   | 53 | PC12          | I/O | FT        | Yes                | I2C2_SCL/<br>I2S1_SD/<br>SPI2_MOSI/<br>UART4_TX/<br>SDIO_CK/<br>DCMI_D9/<br>EVENTOUT         | -    | -  |

| 81   | -  | PD0           | I/O | FT        | Yes                | CAN0_RX/<br>EMC_D2/<br>DCMI_D12                                                              | -    | -  |

| 82   | -  | PD1           | I/O | FT        | Yes                | CAN0_TX/<br>EMC_D3/<br>DCMI_D13/<br>EVENTOUT                                                 | -    | -  |

| 83   | 54 | PD2           | I/O | FT        | Yes                | TIM2_ETR/<br>TIM10_CH2/<br>I2C2_SDA/<br>UART4_RX/<br>ETH_CLK125M_IN<br>SDIO_CMD/<br>DCMI_D11 | -    | -  |

| 84   | -  | PD3           | I/O | FT        | Yes                | TIM10_CH3/<br>UART1_CTS/<br>QSPI_CSN/<br>EMC_A15                                             | -    | -  |

| 85   | -  | PD4           | I/O | FT        | Yes                | TIM10_CH4/<br>UART1_RTS/<br>QSPI_DIO0/<br>EMC_OEN                                            | -    | -  |

| 86   | -  | PD5           | I/O | FT        | Yes                | TIM10_CH1/<br>UART1_TX/<br>QSPI_DIO1/<br>EMC_WEN                                             | -    | -  |

| 87   | -  | PD6           | I/O | FT        | Yes                | TIM10_CH3/<br>UART1_RX/<br>QSPI_DIO2/<br>ETH_TX_ER/<br>EMC_RS                                | -    | -  |

| 引脚编号<br>LQFP100<br>LQFP64 <sup>+</sup> |    | 引脚名称<br>(复位后) | 类型  | I/O<br>结构 | Fail<br>safe<br>支持 | 可选的复用功能                                                                                                          |      | 说明                      |

|----------------------------------------|----|---------------|-----|-----------|--------------------|------------------------------------------------------------------------------------------------------------------|------|-------------------------|

|                                        |    |               |     |           |                    | 复用功能                                                                                                             | 可选功能 |                         |

| 88                                     | -  | PD7           | I/O | FT        | Yes                | TIM12_CH1/<br>QSPI_DIO3/<br>EMC_CS_N0/<br>EVENTOUT                                                               | -    | -                       |

| 89                                     | 55 | PB3           | I/O | FT        | Yes                | JTDO-TRACESWO/<br>TIM1_CH2/<br>SPI0_SCK/<br>SPI2_SCK/<br>I2S1_CK/<br>USART7_CK/<br>TIM12_CH2                     | -    | 默认 JTDO, input floating |

| 90                                     | 56 | PB4           | I/O | FT        | Yes                | NJRST/<br>TIM2_CH1/<br>SPI0_MISO/<br>SPI2_MISO/<br>I2S1_EXTSD/<br>USART7_TX/<br>SDIO_CD                          | -    | 默认 NJRST, 输入, 内部下拉电阻    |

| 91                                     | 57 | PB5           | I/O | FT        | Yes                | TIM2_CH2/<br>I2C0_SDA/<br>SPI0_MOSI/<br>SPI2_MOSI/<br>I2S1_SD/<br>USART7_RX/<br>CAN1_RX/<br>SDIO_WP/<br>DCMI_D10 | -    | -                       |

| 92                                     | 58 | PB6           | I/O | FT        | Yes                | TIM3_CH1/<br>I2C0_SCL/<br>UART0_TX/<br>USART7_CTS/<br>CAN1_TX/<br>SDIO_RSTN/<br>DCMI_D5                          | -    | -                       |

| 引脚编号<br>LQFP100<br>LQFP64 <sup>+</sup> |    | 引脚名称<br>(复位后) | 类型  | I/O<br>结构 | Fail<br>safe<br>支持 | 可选的复用功能                                                                                          |      | 说明           |

|----------------------------------------|----|---------------|-----|-----------|--------------------|--------------------------------------------------------------------------------------------------|------|--------------|

|                                        |    |               |     |           |                    | 复用功能                                                                                             | 可选功能 |              |

| 93                                     | 59 | PB7           | I/O | FT        | Yes                | TIM3_CH2/<br>I2C0_SDA/<br>UART0_RX/<br>USART7_RTS/<br>DCMI_VSYNC/<br>EVENTOUT                    | -    | -            |

| 94                                     | 60 | BOOT0         | I   | B         | Yes                | -                                                                                                | -    | 外部需接上拉或者下拉电阻 |

| 95                                     | 61 | PB8           | I/O | FT        | Yes                | TIM3_CH3/<br>TIM9_CH1/<br>I2C0_SCL/<br>CAN0_RX/<br>ETH_TXD3/<br>SDIO_D4/<br>DCMI_D6              | -    | -            |

| 96                                     | 62 | PB9           | I/O | FT        | Yes                | TIM3_CH4/<br>TIM10_CH1/<br>I2C0_SDA/<br>SPI1_NSS/<br>I2S0_WS/<br>CAN0_TX/<br>SDIO_D5/<br>DCMI_D7 | -    | -            |

| 97                                     | -  | PE0           | I/O | FT        | Yes                | TIM3_ETR/<br>EMC_DQM0/<br>DCMI_D2                                                                | -    | -            |

| 98                                     | -  | PE1           | I/O | FT        | Yes                | EMC_DQM1/<br>DCMI_D3/<br>EVENTOUT                                                                | -    | -            |

注:

- PC13、PC14、PC15 通过电源开关供电。由于该开关的灌电流能力有限 (3 mA)，因此在输出模式下使用 GPIO PC13 到 PC15 时存在以下限制：

- 速率不得超过 2MHz，最大负载为 30pF。

- 这些 I/O 不能用作电流源（如用于驱动 LED）。

2. PA4, PA5 作为 GPIO 使用时, 不建议打开上拉电阻功能。作为 ADC 输入通道采样时, 需要保证采样的模拟信号比较强, 否则不建议作为 ADC 输入通道。

### 3.3 引脚复用定义

表 3-3: 端口 A 引脚复用功能

| 端口  | AF0  | AF1               | AF2          | AF3      | AF4       | AF5      | AF6       | AF7              | AF8       | AF9                      | AF10       | AF11     | AF12                        | AF13       | AF14 | AF15     |

|-----|------|-------------------|--------------|----------|-----------|----------|-----------|------------------|-----------|--------------------------|------------|----------|-----------------------------|------------|------|----------|

|     | SYS  | TIM0/1/<br>LPUART | TIM0/2/4     | TIM7/8/9 | I2C2      | SPI0     | SPI2      | UART0/1/<br>I2S1 | UART3     | CAN0/USART6<br>/TIM12/13 | QSPI       | ETH      | -                           | DCMI       | -    | EVENTOUT |

| 端口A | PA0  | -                 | TIM1_CH1_ETR | TIM4_CH1 | TIM7_ETR  | -        | -         | -                | UART1_CTS | UART3_TX                 | USART6_CTS | -        | ETH_CRS                     | -          | -    | -        |

|     | PA1  | -                 | TIM1_CH2     | TIM4_CH2 | -         | -        | -         | -                | UART1_RTS | UART3_RX                 | USART6_RTS | -        | ETH_RX_CLK<br>(ETH_REF_50M) | -          | -    | EVENTOUT |

|     | PA2  | -                 | TIM1_CH3     | TIM4_CH3 | TIM8_CH1  | -        | -         | -                | UART1_TX  | UART3_CTS                | USART6_TX  | QSPI_CSN | ETH_MDIO                    | -          | -    | -        |

|     | PA3  | -                 | TIM1_CH4     | TIM4_CH4 | TIM8_CH2  | -        | -         | -                | UART1_RX  | UART3_RTS                | USART6_RX  | -        | ETH_COL                     | -          | -    | -        |

|     | PA4  | -                 | LPUART_TX    | TIM0_CH3 | -         | -        | SPI0_NSS  | SPI2_NSS         | -         | I2S1_WS                  | USART6_CK  | -        | -                           | DCMI_HSYNC | -    | -        |

|     | PA5  | -                 | TIM1_CH1_ETR | TIM0_CH4 | TIM7_CH1N | -        | SPI0_SCK  | -                | -         | -                        | TIM12_CH2  | -        | -                           | -          | -    | -        |

|     | PA6  | -                 | TIM0_BKIN    | TIM2_CH1 | TIM7_BKIN | -        | SPI0_MISO | -                | -         | -                        | TIM12_CH1  | -        | -                           | DCMI_PIXCK | -    | -        |

|     | PA7  | -                 | TIM0_CH1N    | TIM2_CH2 | TIM7_CH1N | -        | SPI0_MOSI | -                | -         | -                        | TIM13_CH1  | -        | ETH_RX_DV                   | -          | -    | EVENTOUT |

|     | PA8  | MCO0              | TIM0_CH1     | -        | -         | I2C2_SCL | -         | -                | -         | -                        | -          | -        | -                           | -          | -    | -        |

|     | PA9  | -                 | TIM0_CH2     | -        | -         | I2C2_SDA | -         | -                | UART0_TX  | -                        | -          | -        | -                           | DCMI_D0    | -    | -        |

|     | PA10 | -                 | TIM0_CH3     | -        | -         | -        | -         | -                | UART0_RX  | -                        | -          | -        | -                           | DCMI_D1    | -    | -        |

|     | PA11 | -                 | TIM0_CH4     | -        | -         | -        | -         | -                | UART0_CTS | -                        | CAN0_RX    | -        | -                           | -          | -    | -        |

|     | PA12 | -                 | TIM0_ETR     | -        | -         | -        | -         | -                | UART0_RTS | -                        | CAN0_TX    | -        | -                           | -          | -    | EVENTOUT |

|     | PA13 | JTMS<br>SWDIO     | -            | -        | -         | -        | -         | -                | -         | -                        | -          | -        | -                           | -          | -    | -        |

|     | PA14 | JTCK<br>SWCLK     | -            | -        | -         | -        | -         | -                | -         | -                        | -          | -        | -                           | -          | -    | -        |

|     | PA15 | JTDI              | TIM1_CH1_ETR | -        | TIM9_CH2  | -        | SPI0_NSS  | SPI2_NSS         | I2S1_WS   | -                        | -          | -        | -                           | -          | -    | -        |

表 3-4: 端口 B 引脚复用功能

| 端口   | AF0  | AF1               | AF2               | AF3       | AF4       | AF5       | AF6       | AF7               | AF8             | AF9                 | AF10      | AF11      | AF12         | AF13       | AF14     | AF15     |

|------|------|-------------------|-------------------|-----------|-----------|-----------|-----------|-------------------|-----------------|---------------------|-----------|-----------|--------------|------------|----------|----------|

|      | SYS  | TIM0/1            | TIM2/3/<br>LPUART | TIM7/9/10 | I2C0/1    | SPI0/SPI1 | SPI2/I2S0 | UART0//2/<br>I2S1 | UART5<br>USART7 | CAN0/1/<br>TIM11/12 | QSPI      | ETH       | EMC/<br>SDIO | DCMI       | -        | EVENTOUT |

| 端口 B | PB0  | -                 | TIM0_CH2N         | TIM2_CH3  | TIM7_CH2N | -         | -         | -                 | -               | TIM12_CH3           | -         | ETH_RXD2  | -            | -          | -        | -        |

|      | PB1  | -                 | TIM0_CH3N         | TIM2_CH4  | TIM7_CH3N | -         | -         | -                 | -               | TIM12_CH4           | -         | ETH_RXD3  | -            | -          | -        | EVENTOUT |

|      | PB2  | -                 | -                 | -         | TIM9_CH3  | -         | -         | -                 | -               | TIM12_CH1           | -         | -         | -            | -          | -        | -        |

|      | PB3  | JTDO/<br>TRACESWO | TIM1_CH2          | -         | -         | -         | SPI0_SCK  | SPI2_SCK          | I2S1_CK         | USART7_CK           | TIM12_CH2 | -         | -            | -          | -        | -        |

|      | PB4  | NJTRST            | -                 | TIM2_CH1  | -         | -         | SPI0_MISO | SPI2_MISO         | I2S1_EXTSD      | USART7_TX           | -         | -         | SDIO_CD      | -          | -        | -        |

|      | PB5  | -                 | -                 | TIM2_CH2  | -         | I2C0_SDA  | SPI0_MOSI | SPI2_MOSI         | I2S1_SD         | USART7_RX           | CAN1_RX   | -         | -            | SDIO_WP    | DCMI_D10 | -        |

|      | PB6  | -                 | -                 | TIM3_CH1  | -         | I2C0_SCL  | -         | -                 | UART0_TX        | USART7_CTS          | CAN1_TX   | -         | -            | SDIO_RSTN  | DCMI_D5  | -        |

|      | PB7  | -                 | -                 | TIM3_CH2  | -         | I2C0_SDA  | -         | -                 | UART0_RX        | USART7_RTS          | -         | -         | -            | DCMI_VSYNC | -        | EVENTOUT |

|      | PB8  | -                 | -                 | TIM3_CH3  | TIM9_CH1  | I2C0_SCL  | -         | -                 | -               | CAN0_RX             | -         | ETH_RXD3  | SDIO_D4      | DCMI_D6    | -        | -        |

|      | PB9  | -                 | -                 | TIM3_CH4  | TIM10_CH1 | I2C0_SDA  | SPI1 NSS  | I2S0_WS           | -               | CAN0_TX             | -         | -         | SDIO_D5      | DCMI_D7    | -        | -        |

|      | PB10 | -                 | TIM1_CH3          | LPUART_RX | -         | I2C1_SCL  | SPI1_SCK  | I2S0_CK           | UART2_TX        | -                   | -         | QSPI_SCK  | ETH_RX_ER    | EMC_A0     | -        | -        |

|      | PB11 | -                 | TIM1_CH4          | LPUART_TX | -         | I2C1_SDA  | -         | -                 | UART2_RX        | -                   | -         | -         | ETH_TX_EN    | EMC_A1     | -        | -        |

|      | PB12 | -                 | TIM0_BKIN         | -         | -         | I2C1_SDA  | SPI1 NSS  | I2S0_WS           | -               | UART5_CTS           | CAN1_RX   | TIM11_CH3 | ETH_RXD0     | EMC_A2     | -        | EVENTOUT |

|      | PB13 | -                 | TIM0_CH1N         | -         | -         | -         | SPI1_SCK  | I2S0_CK           | UART2_CTS       | UART5_RTS           | CAN1_TX   | TIM11_CH4 | ETH_RXD1     | EMC_A3     | -        | -        |

|      | PB14 | -                 | TIM0_CH2N         | -         | TIM7_CH2N | I2C1_SCL  | SPI1_MISO | I2S0_EXTSD        | UART2_RTS       | -                   | TIM11_CH1 | -         | -            | -          | -        | -        |

|      | PB15 | -                 | TIM0_CH3N         | -         | TIM7_CH3N | I2C1_SDA  | SPI1_MOSI | I2S0_SD           | -               | -                   | TIM11_CH2 | -         | -            | -          | -        | -        |

表 3-5: 端口 C 引脚复用功能

| 端口   | AF0  | AF1                 | AF2         | AF3      | AF4      | AF5             | AF6             | AF7        | AF8       | AF9        | AF10      | AF11       | AF12         | AF13    | AF14    | AF15     |          |

|------|------|---------------------|-------------|----------|----------|-----------------|-----------------|------------|-----------|------------|-----------|------------|--------------|---------|---------|----------|----------|

|      | SYS  | LPUART/<br>LPTIM0~1 | TIM2/4      | TIM7/9   | I2C2     | SPI1/<br>I2S0/1 | SPI2/<br>I2S0/1 | UART2      | UART3/4/5 | USART6/7   | -         | ETH        | EMC/<br>SDIO | DCMI    | -       | EVENTOUT |          |

| 端口 C | PC0  | -                   | LPTIM0_IN   | TIM4_CH1 | -        | -               | -               | -          | -         | USART6_CTS | -         | -          | EMC_A4       | -       | -       | -        |          |

|      | PC1  | -                   | LPTIM0_OUT  | TIM4_CH2 | -        | -               | -               | -          | -         | USART6 RTS | -         | ETH_MDC    | EMC_A5       | -       | -       | EVENTOUT |          |

|      | PC2  | -                   | LPUART_RX   | TIM4_CH3 | -        | -               | SPI1_MISO       | I2S0_EXTSD | -         | USART6_TX  | -         | ETH_TXD2   | EMC_A6       | -       | -       | -        |          |